# An LLM-Driven Fuzzing Framework for Detecting Logic Instruction Bugs in PLCs

Jiaxing Cheng<sup>†</sup>

Institute of Information

Engineering, CAS; SCS, UCAS

Beijing, China

chengjiaxing@iie.ac.cn

Ming Zhou<sup>†</sup>

SCS, Nanjing University of

Science and Technology

Nanjing, Jiangsu, China

mingzhou@njust.edu.cn

Haining Wang

ECE

Virginia Tech

Arlington, VA, USA

hnw@vt.edu

Xin Chen<sup>\*</sup>

Institute of Information

Engineering, CAS; SCS, UCAS

Beijing, China

chenxin1990@iie.ac.cn

Yuncheng Wang

Institute of Information Engineering

CAS; SCS, UCAS

Beijing, China

wangyuncheng@iie.ac.cn

Yibo Qu

Institute of Information Engineering

CAS; SCS, UCAS

Beijing, China

quyibo@iie.ac.cn

Limin Sun<sup>\*</sup>

Institute of Information Engineering

CAS; SCS, UCAS

Beijing, China

sunlimin@iie.ac.cn

**Abstract**—Programmable Logic Controllers (PLCs) automate industrial operations using vendor-supplied logic instruction libraries compiled into device firmware. These libraries may contain security flaws that, when exploited through physical control routines, network-facing services, or PLC runtime subsystems, may lead to privilege violations, memory corruption, or data leakage. This paper presents LogicFuzz, the first fuzzing framework designed specifically to target logic instructions in PLC firmware. LogicFuzz constructs a semantic dependency graph (SDG) that captures both operational semantics and inter-instruction dependencies in PLC code. Leveraging the SDG together with an enable-signal mechanism, LogicFuzz automatically synthesizes instruction-tailored seed programs, significantly reducing manual effort and enabling controlled, resettable fuzzing on real PLC hardware. To uncover bugs conditioned on control-flow triggers (i.e., invocation patterns), LogicFuzz mutates the SDG to diversify instruction-invocation contexts. To expose data-triggered faults, it performs coverage-guided parameter mutation under valid semantic constraints. In addition, LogicFuzz integrates a multi-source oracle that monitors runtime logs, status LEDs, and communication states to detect instruction-level failures during fuzzing. We evaluate LogicFuzz on six production PLCs from three major vendors and uncover 19 instruction-level bugs, including four previously unknown vulnerabilities.

## I. INTRODUCTION

Programmable Logic Controllers (PLCs) underpin critical infrastructure, including power generation, water treatment, and industrial manufacturing. As societal reliance on these systems grows, faults in PLCs can disrupt essential services and, in severe cases, threaten national security and public safety [9]

[36] [31] [21]. The Triton (TRISIS) attack [17] exemplifies these stakes: adversaries exploited zero-day vulnerabilities in Schneider Electric safety PLCs to tamper with emergency shutdown logic, nearly causing catastrophic damage at a Saudi petrochemical facility.

PLCs execute control programs built from logic instructions that drive physical actuation (e.g., motion control), manage communication interfaces (e.g., Modbus services), and coordinate device-internal subsystems (e.g., memory management). Vendors commonly package these instructions into proprietary firmware-embedded libraries. However, these libraries may contain defects—including unchecked inputs, memory-safety violations (e.g., buffer overflows, null pointer dereferences), and race conditions—introduced through implementation mistakes. When triggered by malformed invocation patterns or adversarial parameters, such bugs can corrupt memory or escalate privileges, endangering the industrial processes the PLC governs [13]. Compounding this risk, vendors frequently reuse instruction libraries across product lines, enabling a single flaw to propagate multiple PLC models.

We propose an automated framework for uncovering logic-instruction bugs in PLC firmware. Conventional static analysis techniques [12] [32] (e.g., taint analysis) are ill-suited for proprietary PLC images: firmware binaries are often stripped, use non-standard formats, and tightly integrate vendor-specific runtime components. As a result, static tools cannot reliably recover code boundaries, data layouts, or calling conventions—context that is essential to modeling instruction semantics. Without this context, they are also unable to infer the data- and control-flow dependencies required for instruction-level bug detection, rendering static approaches largely ineffective on closed PLC platforms. Given these constraints, we turn to fuzzing, which exercises logic instructions through vendor-supported runtime interfaces without requiring visibility into firmware internals. This choice introduces three key challenges that motivate our design.

<sup>†</sup> These authors contributed equally to this work.

<sup>\*</sup> The corresponding authors.

**Challenge 1: Synthesizing semantics-aware seed programs.** Fuzzing logic instruction requires test programs that adhere to usage constraints, hardware side effects (e.g., I/O, timers, watchdogs), and PLC scan-cycle semantics. These behaviors vary significantly across vendors and are poorly documented in closed-source platforms, making manual derivation slow and error-prone. The challenge is to accurately recover instruction-level usage semantics and automatically generate valid, controllable, and resettable seed programs at scale.

**Challenge 2: Feedback-guided exploration without instrumentation.** PLC firmware is proprietary, heterogeneous across architectures and RTOSes, and incompatible with conventional techniques such as instrumentation or binary rewriting—mechanisms that typically supply coverage or state feedback. In the absence of such signals, fuzzers struggle to guide execution toward high-value states and corner cases. The challenge is to extract meaningful, low-noise feedback from vendor-exposed interfaces and runtime artifacts, and to design mutation strategies that effectively leverage this feedback to produce high-quality inputs.

**Challenge 3: Comprehensive anomaly detection beyond crashes.** Logic instruction failures frequently manifest not as crashes but as scan-cycle stalls, I/O inconsistencies, timing violations, watchdog resets, or silent state divergence—behaviors that crash-only oracles systematically miss. Meanwhile, PLCs expose heterogeneous exception signals (e.g., runtime logs, status LEDs, and communication states) that are encoded in vendor-specific ways. The challenge is to build a vendor-agnostic monitoring oracle that fuses these signals to detect a broad spectrum of anomalies while minimizing false positives.

We present **LogicFuzz**, an automated fuzzing framework for PLC logic instructions. To the best of our knowledge, LogicFuzz is the first system to systematically target instruction-level bugs on real PLC hardware. LogicFuzz constructs a lightweight semantic dependency graph (SDG) and couples it with an enable-signal-guided prompting mechanism that steers a large language model (LLM) to generate test programs that are valid, controllable, and resettable while adhering to hardware constraints and instruction semantics. To drive exploration on closed-source devices, LogicFuzz leverages vendor-exposed serial debugging to integrate structural (invocation-pattern) mutation with coverage-guided parameter mutation. It further unifies network behavior, internal system status, and physical actuation feedback into a multi-source anomaly-detection oracle capable of identifying failures beyond conventional crash-based signals.

We evaluate LogicFuzz on six commercial PLC models from three vendors. It successfully generated valid seeds for 88.47% of the targeted instructions and uncovered 19 instruction-level bugs, including four previously undisclosed vulnerabilities. These flaws span both device-control and system-management instructions, with several capable of forcing PLC shutdowns—posing direct physical-safety risks. By exploiting enable signals for precise control and reset, and by combining SDG-based structural mutation with coverage-

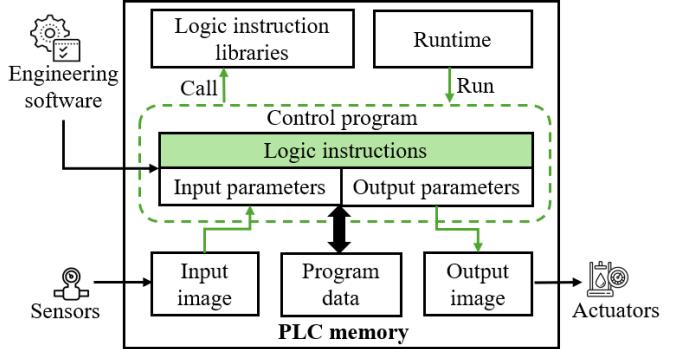

Fig. 1: Execution workflow of PLC logic instructions.

guided parameter mutation, LogicFuzz delivers an instruction-centric fuzzing workflow for real-world PLC platforms.

The remainder of this paper is organized as follows. Section II provides background on PLC logic instructions and motivating observations. Section III presents an overview of the LogicFuzz framework. Sections IV-VI detail the static analysis pipeline, seed program generation, and instruction-level fuzzing. Section VII reports our evaluation results. Section IX discusses insights and limitations. Section VIII surveys related work, and finally, Section X concludes the paper.

## II. BACKGROUND

This section describes how logic instructions are executed in PLCs, identifies two primary classes of instruction vulnerabilities, and explains how the enable-signal mechanism motivates our design.

### A. Runtime Execution of Logic Instructions

Under the IEC 61131-3 standard, control logic can be written in five languages—Ladder Diagram (LD), Function Block Diagram (FBD), Structured Text (ST), Instruction List (IL), and Sequential Function Chart (SFC). In this work, we focus on ST and its Siemens variant, SCL. A typical program executes in three phases. Parameter initialization declares variables and data types. Context initialization prepares run-time state by invoking auxiliary instructions or assigning values. Finally, instruction invocation executes the target logic instruction. This structure conforms to vendor usage constraints. By injecting externally supplied protocol data into the instruction’s parameters, each fuzzing iteration remains aligned with the PLC’s scan cycle, enabling us to exercise every instruction within its native execution context.

When powered on, the PLC loads firmware that manages peripherals, internal resources, and communication interfaces, and then enters a continuous scan cycle (illustrated by the green dashed box and arrow in Figure 1). At the beginning of each cycle, sensor readings are sampled into the *input image*. The control program then fetches operands—either from the *input image* or from the *program data* region—dispatches the corresponding logic instructions from the instruction library, and executes them. The resulting values are written to the

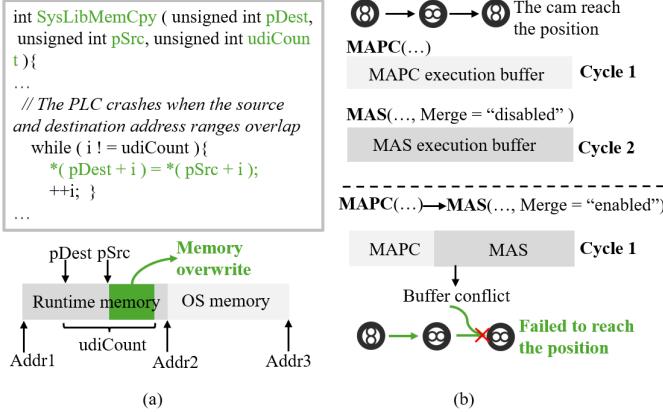

Fig. 2: Logic-instruction bugs are primarily triggered by (a) parameter values and (b) invocation patterns.

*output image* or back to program data; the output image is subsequently mapped to actuators, producing physical effects. During runtime, engineers can feed mutated inputs through the parameter read-write protocol and observe anomalies in multiple channels, including runtime logs, status LEDs, UART output, and Joint Test Action Group (JTAG) traces. Collectively, these signals expose crashes, scan cycle stalls, register corruption, and other instruction-level faults, providing a comprehensive oracle for fuzzing.

### B. Vulnerable Logic Instructions

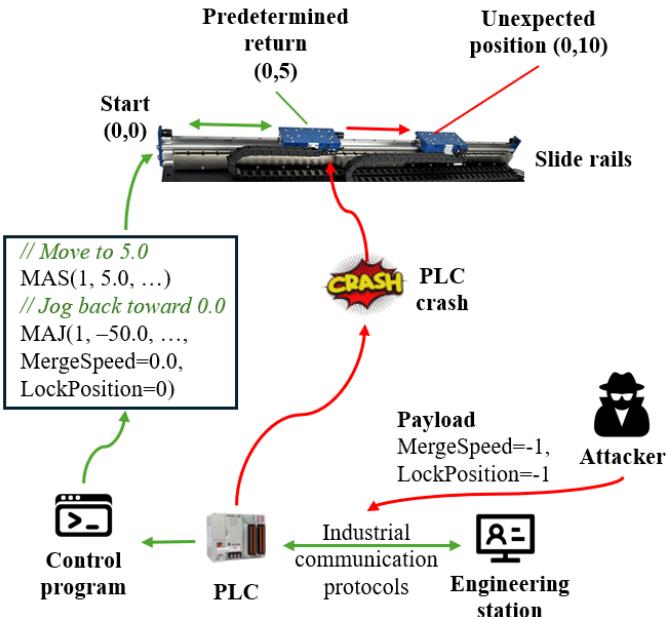

Logic-instruction bugs are firmware-level defects in the implementation of PLC logic instructions. When exercised under vendor-specified contexts and parameter constraints, these flaws can lead to memory corruption, denial-of-service, or unstable physical outputs. Such bugs typically fall into four categories: 1) input-handling errors (e.g., missing type or bounds checks), 2) resource-management faults (e.g., unchecked memory operations), 3) security or access control lapses (e.g., incorrect privilege settings), and 4) business-logic or configuration mistakes (e.g., inadequate functional-safety rules). We observe that vulnerabilities across all four categories are usually triggered by two factors: Parameter values—edge cases or adversarial data, and invocation patterns—the call order and inter-parameter dependencies that govern run-time interactions. Figure 2 (a) illustrates a value-driven flaw: `SysMemcpy` invokes `SysLibMemcpy` without validating either its source (`pSrc`) or destination (`pDest`) pointers. If `pDest < pSrc`, the routine overwrites memory and compromises the PLC.

Figure 2 (b) shows a pattern-driven flaw in Rockwell’s ControlLogix 5570 PLC: Enabling the *merge* option allows the stop command `MAS` to pre-empt an unfinished cam-control command `MAPC`, corrupting its buffer and crashing the controller so that the axis halts short of its intended target. These cases suggest that exposing latent instruction-level bugs requires systematic mutation of both parameters and invocation relationships. LogicFuzz adopts this dual strategy

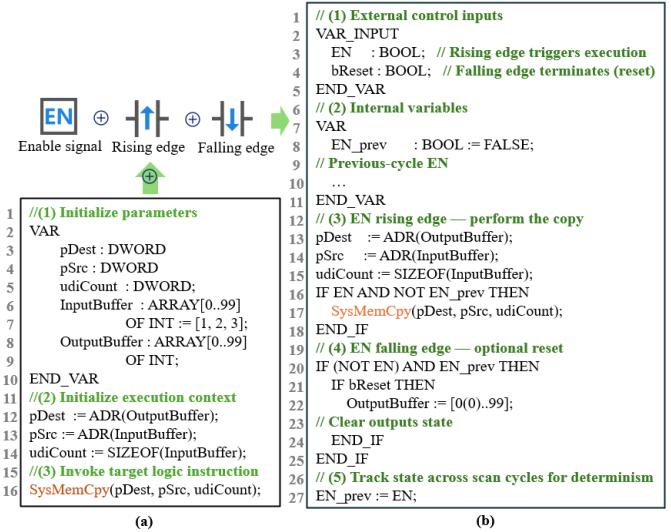

Fig. 3: Two control-program structures for `SysMemcpy`: (a) a representative production-style program; (b) our enable-signal-driven test program.

by interleaving SDG-based semantic mutation with coverage-guided parameter mutation, enabling vulnerability discovery across diverse execution contexts.

### C. Motivation

We refer to the control programs used during fuzzing as test programs. Early experiments with naive layouts revealed that many logic instructions are highly sensitive to PLC runtime resources—including memory buffers, file descriptors, network sockets, timers, persistent variables, and task objects. Consider fuzzing `SysMemcpy`, a memory-resource-sensitive instruction. As shown in Figure 3 (a), if the routine fails to release memory resources, the stale state carries over into subsequent fuzzing rounds. The consequences include false positives, masked bugs that require a clean start to manifest, distorted coverage metrics, and non-reproducible crashes. In contrast, session-oriented instructions (e.g., HTTP services) depend on persistent state and therefore must not be reset each cycle. A reset strategy must therefore be selective and aligned with the PLC scan cycle semantics. Resources are safely cleared only in the following cycle—not the current one—to avoid forcing slower PLCs into premature resource release.

Most vendors embed an enable signal in every logic instruction. The PLC samples this Boolean flag once per scan, and engineers can toggle it over the network to skip or re-trigger the instruction without modifying the program. Leveraging this mechanism, we make each test program both controllable and resettable—even for PLCs lacking a native enable signal—by introducing two external inputs, `EN` and `bReset` (Figure 3.b), together with rising- and falling-edge logic: **Rising edge** (`EN` transitions from `FALSE` to `TRUE`)—fires the instruction exactly once per test case execution. All rising-edge regions share the same `EN`. **Falling edge** (`EN` transitions from `TRUE`

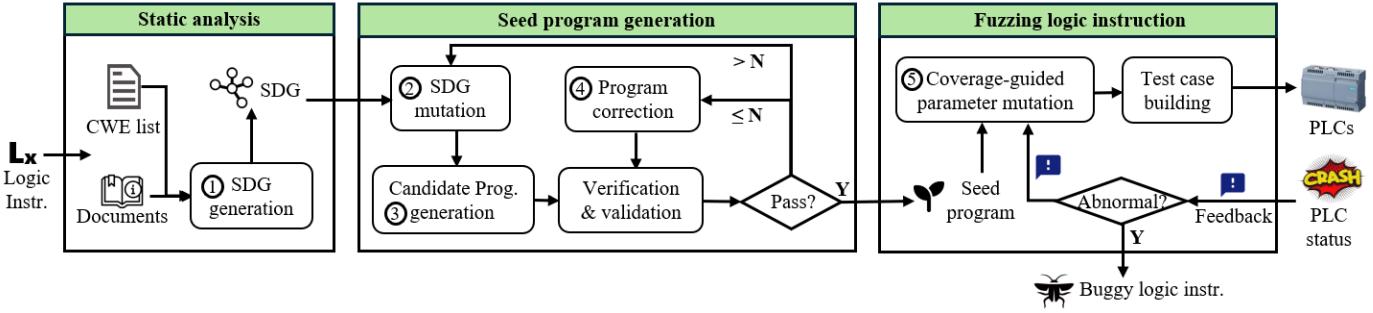

Fig. 4: Overview of LogicFuzz’s workflow.

| Bug clue extraction prompt |                                                                                                                                                                                                                                                                                                                     |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>[Input]</b>             | : Manuals, CWE list, $L_x$                                                                                                                                                                                                                                                                                          |

| <b>[Task]:</b>             | For each CWE entry, assess whether its root cause and triggering conditions are applicable to logic instruction $L_x$ using the provided manuals.                                                                                                                                                                   |

|                            | If applicable, generate one or more concise bug clues.                                                                                                                                                                                                                                                              |

| <b>[Output]:</b>           | Each item in bug clues must be a dictionary with the following fields:                                                                                                                                                                                                                                              |

|                            | <ul style="list-style-type: none"> <li>• "bug_type": a short CWE-relevant bug category.</li> <li>• "trigger_param": the name of a parameter of <math>L_x</math> that is likely to trigger the bug.</li> <li>• "trigger_condition": a suspicious value range or usage condition that may lead to the bug.</li> </ul> |

Fig. 5: LLM prompt for bug-clue extraction.

to FALSE)—checks `bReset`; if TRUE, it reinitialises all internal state (buffers, counters, handles), ensuring a pristine environment for the next cycle. All falling-edge regions share the same `bReset`. Finally, the current `EN` value is latched for the subsequent scan to enable precise, cycle-synchronous control throughout fuzzing.

### III. OVERVIEW

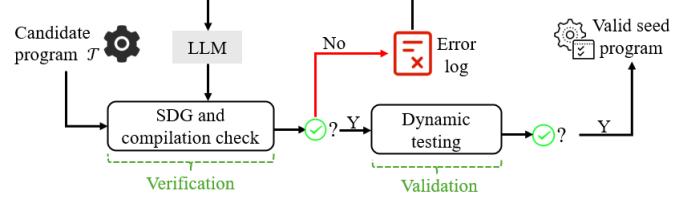

Figure 4 illustrates LogicFuzz’s three-stage workflow. In the first stage, a static preprocessing pass merges vendor documentation with a CWE corpus to construct a semantic dependency graph (SDG) that captures each instruction’s call ordering—including both caller-callee relations and execution sequencing—as well as its parameter dependencies. For each target instruction, LogicFuzz samples an SDG subgraph, mutates it by shuffling calls or rewiring dependencies, and supplies the mutated subgraph—together with a program-generation prompt—to a large language model, which synthesizes a candidate test program. Each generated program is then deployed to the tested PLC for verification. If the program passes validation, it becomes a seed; if it fails, LogicFuzz repeats the mutate–generate–verify loop until success or until

a user-defined limit  $N$  is reached, after which the system starts with a fresh SDG mutation.

During the fuzzing stage, coverage-guided parameter mutation— informed by both the SDG and prior execution feedback—generates new inputs for each seed, which are executed directly on the physical PLC. A monitoring component continuously collects runtime logs, status LED states, and serial output. This feedback simultaneously guides subsequent mutations and serves as an anomaly-detection oracle for crashes, watchdog resets, and silent state corruption.

### IV. STATIC ANALYSIS

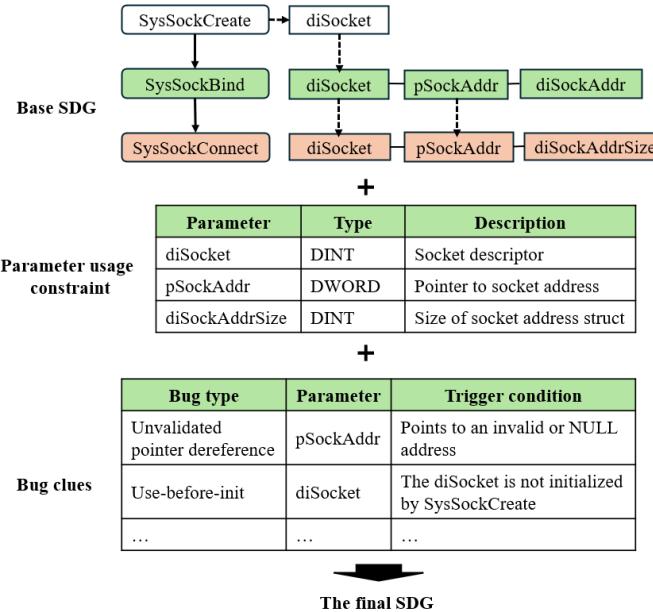

This section explains how LogicFuzz uses static analysis to build a Semantic Dependency Graph (SDG) that captures instruction-usage semantics. The SDG encodes (i) the call order—which covers caller–callee relations and execution sequencing—and parameter dependencies between the target instruction  $L_x$  and other instructions, (ii) per-parameter usage constraints, and (iii) bug clues distilled from the CWE corpus and vendor materials (manuals and example code).

LogicFuzz iterates over Common Weakness Enumeration (CWE) entries collected from MITRE CWE [26]. For each entry—represented by an example, root cause, and potential impact—it queries a large language model (LLM) with the CWE description and the manuals of  $L_x$  (prompt shown in Figure 5) to determine whether the CWE is applicable. We segment manuals by instruction index and initially feed only the section corresponding to the target instruction; cross-instruction segments are then added incrementally as needed to detect inter-instruction dependencies while respecting token limits. If the LLM deems a CWE applicable, it returns a bug clue that specifies the candidate bug type and, for each parameter of  $L_x$ , the conditions or values likely to trigger it. In addition, LogicFuzz utilizes the LLM to derive per-parameter usage constraints from the manuals, formalized as `(parameter, type, description)`.

Using an existing Structured Text (ST) AST extractor [39], LogicFuzz parses the example code of  $L_x$ , splits the statement sequence at control-transfer points (IF/ELSE, loop headers, RETURN/ EXIT) to form basic blocks, and assembles a control-flow graph (CFG). It then performs a standard iterative reaching-definitions analysis on the CFG to recover def-use

Fig. 6: Final SDG for `SysSockConnect`. In the base SDG, dashed edges denote data dependencies, while solid edges represent call and execution flow. Rounded rectangles indicate logic instructions, and rectangular nodes indicate instruction parameters.

relationships. The analysis follows the classical forward data-flow formulation of reaching definitions: For each basic block  $B$ , we iterate

$$IN_B = \bigcup_{P \in \text{pred}(B)} OUT_P \quad (1)$$

$$OUT_B = \text{GEN}_B \cup (IN_B \setminus \text{KILL}_B) \quad (2)$$

to a fixed point, yielding the set of definitions that reach the entry of every block.

During a linear scan of the CFG, each AST node of the form `AssignStmt(... CallExpr(callee="Lk", args=[a1, a2])` induces the following SDG edges: a) A *caller-callee edge* from the current caller to  $L_k$ . b) For every variable argument  $v \in \{a_i\}$ , a set of *parameter-dependency edges*  $d \xrightarrow{(v)} L_k$  for all reaching definitions  $d \in IN_B(v)$ ; literal arguments are instead recorded as edge attributes without creating data-dependency edges. and c) An *execution-order edge*  $L_{\text{prev}} \rightarrow L_k$ , where  $L_{\text{prev}}$  is the most recent instruction call encountered in program order within the same basic block. The collected caller-callee, parameter-dependency, and execution-order edges form the basic SDG. Finally, LogicFuzz attaches the extracted bug clues and the per-parameter usage constraints to the corresponding nodes and edges to obtain the full SDG. An example SDG for `SysSockConnect` is shown in Figure 6. The SDG comprises three components: the basic SDG structure, parameter-usage constraints, and bug clues ("+" denotes conjunction). The basic SDG specifies that `SysSockConnect` requires prior invocations of

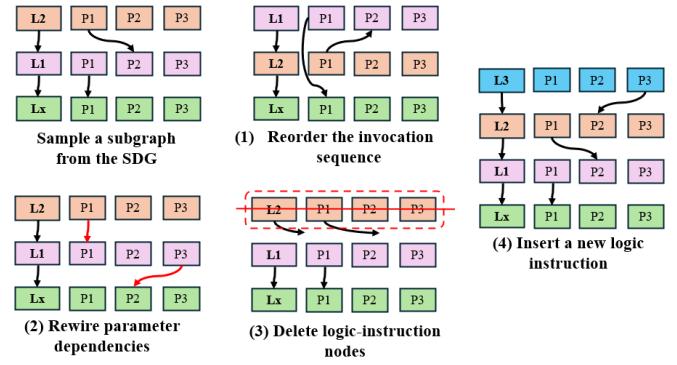

Fig. 7: Four SDG mutation operators.  $L_i$  denotes a logic instruction, and  $P_i$  denotes an instruction parameter.

`SysSockCreate` and `SysSockBind` to create and bind a socket before establishing a connection. The parameter-usage constraints capture the types and usage semantics of the instruction's three parameters, while the attached bug clues indicate the LLM-identified parameter values or conditions that may trigger potential vulnerabilities.

## V. SEED PROGRAM GENERATION

Seed program generation proceeds in three steps: LogicFuzz first mutates the semantic dependency graph (SDG), then synthesizes a candidate program from the mutated subgraph, and finally executes a verify-correct-validate loop to obtain a compilable, semantics-conformant seed.

### A. SDG Mutation

LogicFuzz begins by sampling a subgraph  $g$  from the target logic instruction  $L_x$ 's SDG. If a synthesized program fails verification or validation, LogicFuzz randomly applies one of four mutation operators (Figure 7) to expose  $L_x$  to diverse execution contexts:

- **Reorder:** Permutes the invocation path leading to  $L_x$  while preserving each instruction's associated parameter-dependency edges.

- **Rewire:** Preserves call order but redirects parameter-dependency edges to different instructions and/or argument positions.

- **Delete:** Removes selected instruction nodes and their incident edges. Predecessors and successors retain their original ordering, while affected parameter edges become temporarily unbound.

- **Insert:** Samples a new instruction from the global pool, inserts it at a random position in  $g$  without altering existing dependencies, and randomly attaches its parameter edges to surrounding nodes.

### B. LLM-based Candidate Program Synthesis

Given the mutated subgraph  $g$  and the full SDG, LogicFuzz queries an LLM (prompt in Figure 8) to synthesize a candidate test program  $\mathcal{T}$  following the enable-signal-based template:

$$\mathcal{T} = \langle t_{\text{in}}, t_{\text{var}}, t_{\uparrow}, t_{\downarrow}, t_{\text{st}} \rangle. \quad (3)$$

| Candidate program generation prompt                                                                                                                                                                                                                           |                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>[Input]</b>                                                                                                                                                                                                                                                | : $g', L_x$ , SDG                                                                                                                                                                                                          |

| <b>[Instruction]</b>                                                                                                                                                                                                                                          | Please generate an IEC 61131-3 Structured Text test program $\mathcal{T}$ for the target logic instruction $L_x$ based on the provided SDG. The program must strictly follow the program structure and requirements below: |

| <b>Program structure:</b>                                                                                                                                                                                                                                     | $\mathcal{T} \triangleq \langle A_{in}, A_{var}, A_{\uparrow}, A_{\downarrow}, A_{st} \rangle$                                                                                                                             |

| $A_{in} \triangleq (EN : \text{BOOL}, bReset : \text{BOOL}, \mathfrak{P} = \{p_1 \dots p_n\})$                                                                                                                                                                |                                                                                                                                                                                                                            |

| $A_{var} \triangleq (EN_{\text{prev}} : \text{BOOL} := \text{FALSE}, \text{Ctx} : \Sigma)$                                                                                                                                                                    |                                                                                                                                                                                                                            |

| $A_{\uparrow} (\text{rising edge}) := \{\text{guard} : EN \wedge \neg EN_{\text{prev}}; \text{action} : \Phi(g', \mathfrak{P})\}$<br>where $\Phi(g', \mathfrak{P}) \triangleq \text{Seq}\{L_i(\text{Args}_i) \mid (v_i, \text{Args}_i) \in \text{topo}(g')\}$ |                                                                                                                                                                                                                            |

| $A_{\downarrow} (\text{falling edge}) := \{\text{guard} : \neg EN \wedge EN_{\text{prev}}; \text{action} : \text{if } bReset \text{ then Reset}(\text{Ctx}) \text{ fi}\}$                                                                                     |                                                                                                                                                                                                                            |

| $A_{st} (\text{state tracking}) := \{\text{action} : EN_{\text{prev}} \leftarrow EN\}$                                                                                                                                                                        |                                                                                                                                                                                                                            |

Fig. 8: LLM prompt for candidate-program synthesis.

Inputs  $t_{in} \triangleq (EN : \text{BOOL}, bReset : \text{BOOL}, \mathfrak{P} = \{p_1, \dots, p_n\})$  declares the enable signal, reset flag, and all external parameters required by instructions in  $g$ , ensuring parameter completeness and successful compilation. State  $t_{var} \triangleq (EN_{\text{prev}} : \text{BOOL} := \text{FALSE}, \text{Ctx} : \Sigma)$  maintains cross-cycle context, where  $EN_{\text{prev}}$  supports edge detection and  $\text{Ctx}$  stores subgraph-specific state (e.g., buffers, handles, counters). Rising-edge block  $t_{\uparrow} \triangleq \{\text{guard} : EN \wedge \neg EN_{\text{prev}}; \text{action} : \Phi(g, \mathfrak{P})\}$  fires exactly once per cycle and executes  $\Phi(g, \mathfrak{P}) \triangleq \text{Seq}\{L_i(\text{Args}_i) \mid (v_i, \text{Args}_i) \in \text{topo}(g)\}$ , where  $\text{topo}(g)$  is a topological order of  $g$  and  $\text{Args}_i$  are resolved from  $\mathfrak{P}$ . Falling-edge block  $t_{\downarrow} \triangleq \{\text{guard} : \neg EN \wedge EN_{\text{prev}}; \text{action} : \text{if } bReset \text{ then Reset}(\text{Ctx}) \text{ fi}\}$  conditionally reinitializes internal state to support both persistent-state and immediate-cleanup fuzzing modes. A final State latching block  $t_{st}$  records the current  $EN$  value into  $EN_{\text{prev}}$ , ensuring strict alignment with PLC scan-cycle semantics.

### C. Program Verification and Correction

The LLM-generated program  $\mathcal{T}$  may contain syntactic or semantic defects and must be validated before use. LogicFuzz combines compilation, SDG conformance checking, and automated correction into a unified verification loop (Figure 9). LogicFuzz first compiles  $\mathcal{T}$ . If compilation fails, the compiler error log  $e$  is sent to the correction prompt to guide the LLLM in revising  $\mathcal{T}$ . The revision must satisfy:

- 1) **Syntactic and semantic correctness:**  $\mathcal{T} \in \mathcal{R}$ , where  $\mathcal{R}$  is the IEC 61131-3 ST grammar and semantic constraint set [38].

- 2) **Elimination of the reported failure:**  $\mathcal{T} \not\models e$ .

- 3) **Preservation of program semantics:**  $\text{Semantic}(\text{new } \mathcal{T}) = \text{Semantic}(\mathcal{T})$ .

LogicFuzz retries compilation and correction up to a limit of  $N = 5$ . If compilation still fails,  $\mathcal{T}$  is discarded. LogicFuzz performs the reaching-definitions analysis from Section IV to extract the basic SDG  $g'$  from  $\mathcal{T}$ . It then checks equivalence between  $g'$  and the mutated subgraph  $g$ —including node sets, call ordering, and parameter-dependency relations. Non-conforming programs are discarded.

| Program correction prompt |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>[Input]</b>            | : candidate seed program $\mathcal{T}$ , error log $e$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>[Instruction]</b>      | Given a candidate program $\mathcal{T} \in \mathcal{R}$ and an error log $e \in \mathcal{E}$ :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | <ul style="list-style-type: none"> <li>Identify the root cause <math>\delta</math> from <math>\mathcal{T}</math> and <math>e</math></li> <li>Correct <math>\mathcal{T}</math> according to <math>\delta</math>, ensuring the corrected program strictly complies with the following structure:           <ul style="list-style-type: none"> <li><math>\mathcal{T} \in \mathcal{R}</math> (valid syntax and semantics)</li> <li><math>\mathcal{T} \not\models e</math> (does not reproduce the same failure)</li> <li><math>\text{Semantic}(\text{new } \mathcal{T}) = \text{Semantic}(\mathcal{T})</math></li> </ul> </li> </ul> |

Fig. 9: Program verification-correction-and-validation workflow.

**Program validation.** LogicFuzz next performs short-term dynamic testing to confirm  $\mathcal{T}$ 's functional correctness. The program is deployed to the PLC, a live connection is established, and predefined test inputs are executed:

$$I_i = \langle EN_i, \text{RESET}_i, \text{PARAM}_i \rangle.$$

For each input, LogicFuzz defines an invalidation oracle:

$$\text{oracle}_i = F_{\log_i} \cup F_{\text{param}_i} \cup F_{\text{coverage}_i} \cup F_{\text{snapshot}_i},$$

where:  $F_{\log_i}$  is the runtime log produced by engineering tools,  $F_{\text{param}_i}$  records observed input/state values,  $F_{\text{coverage}_i}$  is derived from PC traces via the serial port or JTAG (Section VI-A),  $F_{\text{snapshot}_i}$  captures PLC state snapshots before and after execution (e.g., memory, handles, timers).

If any predicate in  $\text{oracle}_i$  is triggered,  $\mathcal{T}$  is deemed functionally invalid and discarded. Only programs that pass all oracles are accepted as seeds  $\mathcal{T}_s$ .

We employ four inputs and corresponding oracles:

- $I_0 = \langle \text{True}, \text{False}, \emptyset \rangle$  (baseline rising-edge skeleton). Invalidation: log contains “error/crash/failure”; unexpected parameter/state changes; empty coverage; unchanged snapshots.

- $I_1$  Normal invocation with valid parameters. Invalidation: identical to  $I_0$  plus: no expected state updates; no coverage increase; unchanged snapshot (indicating  $L_x$  did not execute).

- $I_2$  Repeats  $I_1$  for one minute to expose latent leaks/timeouts; invalidation predicates identical to  $I_1$ .

- $I_3 = \langle \text{False}, \text{True}, \emptyset \rangle$  (falling-edge reset). Invalidation: reset effects absent; empty coverage; unchanged snapshot.

Only candidates that pass all runtime oracles are promoted as seeds for subsequent fuzzing.

## VI. LOGIC INSTRUCTION FUZZING

For each seed program  $\mathcal{T}_s$ , LogicFuzz performs parameter fuzzing to further explore bugs in the target instruction  $L_x$ .

---

**Algorithm 1** Coverage-Guided Parameter Mutation

**Require:** Parameter set  $\mathcal{P}$ , mutation pool  $\mathcal{M}$ , subset size  $l$ , UCB constant  $C$ , log weight  $\beta$

- 1:  $cov \leftarrow 0; K \leftarrow 0$   $\triangleright$  **Step 0:** Initialize the global round counter.

- 2: **for all**  $p_i \in \mathcal{P}$  **do**  $\triangleright$  **Step 0:** Initialize the bandit stats.

- 3:  $n_i \leftarrow 0; R_i \leftarrow 0$

- 4: **end for**

- 5: **while not**  $\text{STOP}(K, cov)$  **do**

- 6:   **for all**  $p_i \in \mathcal{P}$  **do**  $\triangleright$  **Step 1:** Compute the UCB score.

- 7:      $\text{score}_i \leftarrow \text{UCBSCORE}(n_i, R_i, C, K)$

- 8:   **end for**

- 9:    $S_K \leftarrow \text{TOP}(\{\text{score}_i\}, l)$   $\triangleright$  **Step 2:** Select top- $l$  parameters.

- 10:   **for all**  $p \in S_K$  **do**  $\triangleright$  **Step 3:** Parameter mutation.

- 11:      $m \leftarrow \text{RANDOMPICK}(\mathcal{M})$

- 12:      $\text{MUTATE}(p, m)$

- 13:   **end for**

- 14:    $(newCov, \log) \leftarrow \text{EXECUTEANDGETCOVERAGE}$   $\triangleright$  **Step 4:** Execute the test case and collect runtime feedback.

- 15:    $\Delta_{\text{cov}} \leftarrow newCov - cov; cov \leftarrow newCov$

- 16:    $\logScore \leftarrow (\log = \emptyset) ? 0 : \text{SCORELLM}(\log)$

- 17:    $r \leftarrow \Delta_{\text{cov}} + \beta \cdot \logScore$   $\triangleright$  **Step 5:** Compute blended reward

- 18:   **for all**  $p_i \in S_K$  **do**

- 19:      $n_i \leftarrow n_i + 1; R_i \leftarrow R_i + \frac{r}{|S_K|}$

- 20:   **end for**

- 21:    $K \leftarrow K + 1$   $\triangleright$  **Step 6:** Update  $K$ .

- 22: **end while**

---

This section describes the design of our coverage-guided parameter mutation strategy, the enable- and reset-based execution control mechanism, and the runtime monitoring infrastructure.

#### A. Coverage-guided parameter mutation

Algorithm 1 adaptively steers mutations toward unexplored firmware regions with high bug potential by leveraging feedback from coverage traces ( $F_{\text{coverage}}$ ) and runtime logs ( $F_{\text{log}}$ ). At initialization, LogicFuzz maintains *per-parameter bandit statistics*—the selection count  $n_i$  and cumulative reward  $R_i$ —under a multi-armed bandit (MAB) model, where each parameter is treated as an arm. Mutation scheduling follows the Upper Confidence Bound (UCB) policy [3]:

$$\text{Score}_i = \frac{R_i}{n_i} + C \cdot \sqrt{\frac{2 \ln K}{n_i}}, \quad (4)$$

where the empirical mean  $\frac{R_i}{n_i}$  captures a parameter’s historical contribution to coverage gains or log anomalies, the second term encourages exploration,  $K$  denotes the current round, and  $C$  controls the exploration–exploitation trade-off. In each round, LogicFuzz selects the top- $l$  parameters according to their UCB score.

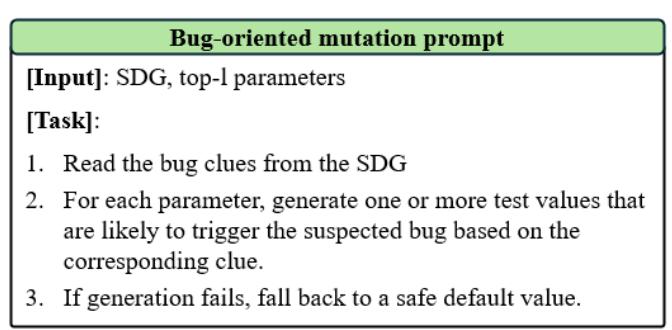

For each selected parameter, LogicFuzz samples a mutation strategy from a pool comprising two behaviors: (i) *Random mutation*, which draws values from the parameter’s full, type-specific domain (e.g.,  $\text{INT} \in [-32,768, 32,767]$ ), or strings as random byte sequences; and (ii) *bug-oriented mutation*, which uses the prompt in Figure 10 to instruct the LLM to analyze  $L_x$ ’s SDG, including parameters, dependencies, and CWE-derived bug clues. The LLM interprets the bug clue and

**↓**

**Mutated top- $l$  parameters of SysSockConnect** **"CWE-119":** {

"diAddressFamily": 2, "diType": 0,

"diProtocol": 10, "pSockAddr":

"127.0.0.1", "diSockAddrSize": 5000}

Fig. 10: LLM prompt for bug-oriented parameter mutation.

proposes values likely to trigger the vulnerability for the top- $l$  parameters, falling back to safe default values if no triggerable inputs are identified.

The generated values are applied via the online write protocol to construct a test case, which is then executed on the PLC. During execution, LogicFuzz collects  $F_{\text{log}}$  and  $F_{\text{coverage}}$  through the engineering software and via serial or Joint Test Action Group (JTAG) interfaces. Since fine-grained basic-block coverage is impractical for PLC firmware without heavy instrumentation [6], [18], we approximate coverage using *memory-block coverage*. PLC memory is partitioned into fixed-size blocks of 50 bytes, corresponding to the average basic-block size in PLC instruction libraries. At the end of  $L_x$ ’s execution cycle, LogicFuzz retrieves the program counter (PC) trace—a sequence of instruction addresses—via the serial port or JTAG interface. Each address is mapped to its corresponding memory block, and a block is marked as hit if at least one address falls within its range. Coverage is computed as:

$$\text{newCov} = \frac{1}{N_{\text{blk}}} \sum_{i=1}^{N_{\text{blk}}} \mathbb{1}(h_i > 0), \quad (5)$$

where  $N_{\text{blk}}$  is the total number of memory blocks,  $h_i$  denotes the hit count of block  $i$ , and  $\mathbb{1}(h_i > 0)$  is the indicator function:

$$\mathbb{1}(h_i > 0) = \begin{cases} 1, & \text{if } h_i > 0, \\ 0, & \text{otherwise.} \end{cases} \quad (6)$$

To exploit semantic signals, LogicFuzz prompts the LLM (Figure 11) to analyze  $F_{\text{log}}$  and produce a likelihood score  $\logScore \in [0, 1]$  accompanied by a brief rationale. The prompt guides the LLM to: (i) analyze runtime logs collected from a real PLC, including resource usage, return codes, fault indicators, and abnormal patterns; (ii) assess whether the logs suggest internal failures or unexpected behavior; and (iii) output a confidence score with supporting textual reasoning.

| Log scoring prompt                                                                                                                                                                                                                                                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>[Input]</b> : $F_{\log}$                                                                                                                                                                                                                                                           |  |

| <b>[Task]:</b>                                                                                                                                                                                                                                                                        |  |

| You are given a runtime log collected by executing a logic instruction with specific parameters on a real PLC. The log may include:                                                                                                                                                   |  |

| <ul style="list-style-type: none"> <li>• Resource usage (CPU, memory)</li> <li>• Execution time and scan-cycle behavior</li> <li>• Function return values or status codes</li> <li>• Exception messages or fault indicators</li> <li>• Abnormal patterns or assertion logs</li> </ul> |  |

| <b>Your task is to:</b>                                                                                                                                                                                                                                                               |  |

| (1) Carefully analyze the log.                                                                                                                                                                                                                                                        |  |

| (2) Based on the PLC runtime states in the log, assess the likelihood that the logic instruction triggered an internal bug and output a probability score, $\text{logScore} \in [0,1]$ .                                                                                              |  |

| (3) Briefly explain your reasoning.                                                                                                                                                                                                                                                   |  |

"`logScore`": 0.85,

"`Reason`": "The log shows intermittent scan-cycle overruns. This pattern suggests a potential failure mode (e.g., a timing-related issue), indicating a high likelihood of an internal fault."

Fig. 11: LLM prompt for log scoring ( $\text{logScore} \in [0,1]$ ) estimates the likelihood that the logic instruction triggered an internal bug).

The round reward integrates both structural and semantic feedback:

$$r = \Delta_{\text{cov}} + \beta \cdot \text{logScore}. \quad (7)$$

To mitigate stagnation caused by deterministic logs and prevent  $\text{logScore}$  from dominating the reward, LogicFuzz randomizes  $\beta \sim \mathcal{U}(0,1]$ , improving robustness across rounds. The reward  $r$  is evenly assigned to all mutated parameters to update their corresponding  $n_i$  and  $R_i$ . As  $K$  increases, the scheduler progressively prioritizes parameters that consistently improve coverage or elicit anomalous behavior, enabling deeper exploration of PLC execution paths.

### B. Enable and Reset Control Mechanism

The enable signal `EN` and reset signal `bReset` are not subjected to mutation; instead, they serve as deterministic global controls governing the start, execution, and reset of each fuzzing test case. Before fuzzing begins, all control variables are initialized to `EN = FALSE` and `bReset = FALSE`. For each mutated test case, LogicFuzz first records a complete snapshot of the PLC state, including memory contents, system handles, and active timers. The fuzzer then sets signal `EN` to `TRUE`, triggering a single instruction execution.

After execution, LogicFuzz captures a second state snapshot and resets `EN` to `FALSE`. Based on a hierarchical reset policy, the fuzzer decides whether to assert `bReset = TRUE` to restore the PLC to a known state. A reset is triggered under any of the following conditions: (i) the monitoring module detects an anomaly, causing an immediate PLC restart; (ii) the pre- and post-execution snapshots are identical, indicating no

TABLE I: Hardware and software configuration for evaluating LOGICFUZZ.

| Category             | Vendor    | Detail                                                                                         |

|----------------------|-----------|------------------------------------------------------------------------------------------------|

| PLCs                 | Rockwell  | CompactLogix 1756-L61 (firmware versions 16.023, 17.004, 19.015, 20.014)                       |

|                      |           | CompactLogix 1756-L33ER (firmware versions 20.011, 20.015, 24.011, 24.013)                     |

|                      | Siemens   | S7-1200 (firmware versions 3.0.2, 4.3.2, 4.4.2)                                                |

|                      |           | S7-1500 (firmware versions 1.5, 1.7, 2.9, 3.1)                                                 |

|                      | Wago      | PFC 750-8203 (firmware versions 1.02.05, 02.03.09)                                             |

|                      |           | 758-870 (firmware version 3.00)                                                                |

| Engineering software | Rockwell  | RSLogix 5000                                                                                   |

|                      | Siemens   | TIA Portal V14                                                                                 |

|                      | Wago      | CODESYS 2.3                                                                                    |

| Logic instructions   | Rockwell  | Total: 112 (External physical control: 77; Internal system operations: 34; Communication: 1).  |

|                      | Siemens   | Total: 126 (External physical control: 42; Internal system operations: 64; Communication: 20). |

|                      | Wago      | Total: 100 (External physical control: 37; Internal system operations: 36; Communication: 27). |

| LLMs                 | OpenAI    | GPT-4o                                                                                         |

|                      | Deepseek  | Deepseek-R1                                                                                    |

|                      | Anthropic | Claude Sonnet 4                                                                                |

observable state change; or (iii) the condition `resetScore = a · x + b · y > 0.5` holds, where  $a$  and  $b$  are LLM-inferred likelihoods that the instruction is resource-sensitive or session-persistent, respectively, and  $x$  and  $y$  are random values sampled from  $[0, 1]$ .

Upon receiving a reset signal, LogicFuzz invokes the reset module embedded in the seed program to restore the PLC state. If this reset fails—i.e., the pre- and post-reset snapshots remain unchanged—LogicFuzz escalates to a program-level reset using the engineering software’s APIs to explicitly restore memory, handles, and timers. For example, LogicFuzz may invoke PLC memory-reset interfaces such as `SysMemSet` in CODESYS or `POKE_BLK` in Siemens environments to overwrite arbitrary memory regions. If the program-level reset also fails, the PLC is forcibly rebooted and fuzzing resumes from a clean state. This dual-layer reset design mitigates potential implementation errors in the reset module and ensures that the PLC reliably returns to a consistent, known state between fuzzing iterations.

### C. Anomaly Detection

LogicFuzz defines a set of monitoring oracles  $M_{\text{oracle}}$  derived from three complementary feedback channels—program runtime logs ( $F_{\log}$ ), PLC system indicators ( $F_{\text{light}}$ ), and communication interfaces ( $F_{\text{comm}}$ )—to detect crashes, hangs, and timeouts:

$$M_{\text{oracle}} = F_{\log} \cup F_{\text{light}} \cup F_{\text{comm}}. \quad (8)$$

Guided by vendor documentation on execution failures, system faults, communication errors, and control malfunctions, we implemented 56 reusable oracles spanning three service categories: (1) External physical control (21 oracles), capturing hardware-module and CPU-level faults; (2) Commu-

TABLE II: Logic-instruction bugs discovered by LOGICFUZZ.

| Bug ID         | Logic Instr.     | Function         | Bug type                          | Bug triggering conditions                                                    | Affected PLC        | Version        | Security risk        |

|----------------|------------------|------------------|-----------------------------------|------------------------------------------------------------------------------|---------------------|----------------|----------------------|

| Lgx169520      | GSV              | System operation | Lack of boundary checks           | Set the WCT to year 1900.                                                    | Rockwell 1756-L61   | 17.004, 19.015 | Denial of Service    |

| Lgx179778      |                  |                  |                                   | Set the WCT to year 9999.                                                    | Rockwell 1756-L61   | 20.014         | Denial of Service    |

| Lgx169520      | SSV              | System operation | Lack of boundary checks           | Set the WCT to year 1900.                                                    | Rockwell 1756-L61   | 17.004, 19.015 | Denial of Service    |

| Lgx179778      |                  |                  |                                   | Set the WCT to year 9999.                                                    | Rockwell 1756-L61   | 20.014         | Denial of Service    |

| IN25781        | ALMA             | System operation | Incorrect data type handling      | Set ALMA's tag length to 100.                                                | Rockwell 1756-L61   | 19.015         | Memory corruption    |

| Lgx135333      |                  |                  |                                   | Set ALMA's tag length to -1.                                                 | Rockwell 1769-L33ER | 17.08          | MNRF                 |

| IN25781        | ALMD             | System operation | Incorrect data type handling      | Set ALMA's tag length to 100.                                                | Rockwell 1756-L61   | 19.015         | Memory corruption    |

| Lgx135333      |                  |                  |                                   | Set ALMA's tag length to -1.                                                 | Rockwell 1769-L33ER | 17.08          | MNRF                 |

| Lgx00136317    | MAJ              | Physical control | Improper Parameter Initialization | Set MergeSpeed and LockPosition to -1.                                       | Rockwell 1756-L61   | 20.013, 20.014 | Denial of Service    |

| New            | MRP              | Physical control | Unoptimized Logic                 | Set CurrentPosition + MRPPosition to exceed the maximum representable range. | Rockwell 1756-L61   | 16.023, 17.004 | Denial of Service    |

| CVE-2020-15782 | MOVE_BLK_VARIANT | System operation | Lack of boundary checks           | Make the SRC and DEST arrays overlap.                                        | Siemens S7-1200     | 3.0.2, 3.3.4   | Information exposure |

|                |                  |                  |                                   |                                                                              | Siemens S7-1500     | 1.5            | Information exposure |

| New            | MOVE_BLK         | System operation | Lack of boundary checks           | Use overlapping SRC and DEST addresses.                                      | Siemens S7-1200     | 3.0.2, 3.3.4   | Information exposure |

|                |                  |                  |                                   |                                                                              | Siemens S7-1500     | 1.5            | Information exposure |

| WAGO-2021-01   | SysMemCpy        | System operation | Lack of boundary checks           | Use overlapping pSrc and pDest addresses.                                    | Wago 750-8203       | 3.0            | Memory overflow      |

|                |                  |                  |                                   |                                                                              | Wago 758-870        | 1.02           | Memory overflow      |

| WAGO-2021-02   | Memcpy           | System operation | Lack of boundary checks           | Use overlapping pbSrc and pbyDest addresses.                                 | Wago 750-8203       | 3.0            | Memory overflow      |

|                |                  |                  |                                   |                                                                              | Wago 758-870        | 1.02           | Memory overflow      |

| WAGO-2021-03   | SysMemMove       | System operation | Lack of boundary checks           | Use overlapping pSrc and pDest addresses.                                    | Wago 750-8203       | 3.0            | Memory overflow      |

|                |                  |                  |                                   |                                                                              | Wago 758-870        | 1.02           | Memory overflow      |

| WAGO-2021-04   | MemMove          | System operation | Lack of boundary checks           | Use overlapping pSrc and pDest addresses.                                    | Wago 750-8203       | 3.0            | Memory overflow      |

|                |                  |                  |                                   |                                                                              | Wago 758-870        | 1.02           | Memory overflow      |

| WAGO-2021-05   | SysMemSet        | System operation | Memory access violation           | Out-of-bounds length (udiCount).                                             | Wago 750-8203       | 3.0            | Information exposure |

|                |                  |                  |                                   |                                                                              | Wago 758-870        | 1.02           | Information exposure |

| New            | SysFileWrite     | System operation | Unauthorized access               | Out-of-bounds pointer (buffer).                                              | Wago 750-8203       | 3.0            | Code injection       |

|                |                  |                  |                                   |                                                                              | Wago 758-870        | 1.02           | Code injection       |

| New            | SysFileRead      | System operation | Unauthorized access               | Out-of-bounds pointer (buffer).                                              | Wago 750-8203       | 3.0            | Information exposure |

|                |                  |                  |                                   |                                                                              | Wago 758-870        | 1.02           | Information exposure |

nication services (19 oracles) covering 11 industrial protocols, including disconnects, timeouts, checksum mismatches, and station loss; and (3) Internal system services (16 oracles) monitoring file systems, operating system components, and internal databases. As an illustrative example, a Modbus anomaly is reported if *any* of the following conditions holds: (i) the module fails to respond or times out after a standard request (e.g., function code 0x03); (ii) the device status LED indicates a network error (commonly red, depending on the PLC model); or (iii) the runtime log contains a “Modbus service error/exception.”

For confirmed bugs, LogicFuzz performs root-cause analysis by replaying the proof-of-concept (PoC) input, recording PC traces via the serial interface, reconstructing the executed basic-block sequence, and reverse-engineering the corresponding firmware regions. This process enables manual auditing to verify that the vulnerability is consistently triggerable under the PoC’s constraints.

## VII. EVALUATION

We first describe our experimental setup, then evaluate LogicFuzz’s effectiveness on logic-instruction bugs, ablate five components, compare key design choices against prior work, and finally quantify the impact of exploitation. LogicFuzz consists of roughly 3,000 lines of Python and AutoIt.

### A. Experiment Setting

We use `pdfplumber` [30] to convert PLC manuals [35] [4] [1] into machine-readable text for LLM consumption. All LLM-driven steps—bug-clue extraction for SDG construction,

seed synthesis, and program correction—are implemented via the Python OpenAI library [28]. We import synthesized seed programs into vendor engineering suites (RSLogix5000, TIA Portal V14, and CODESYS 2.3) and use Autolt to automate validation: `Send("v")` pastes the program and `ControlClick` triggers verification. Our fuzzing engine is built on Boofuzz [5]. Following RLPatch [44] and Cojocar et al. [14], we locate JTAG pinouts on Rockwell and Siemens PLCs and use a Segger J-Link to extract debug traces. For WAGO PLCs, we enable root-level SSH access and use `perf` to collect PC traces during fuzzing. For WAGO, we serialize test cases using Boofuzz `Fields`. For Siemens and Rockwell, we deliver test cases via vendor-specific interfaces: `db_write` from `Snap7` and `LogixDriver.write` from `pycomm3`, respectively.

As summarized in Table I, our evaluation covers 338 logic instructions from vendor manuals—112 Siemens, 126 Rockwell, and 100 WAGO—spanning external control, internal system services, and communications. We evaluate two PLC models per vendor across different firmware versions: WAGO PFC 750-8203 and 758-870; Siemens S7-1200 and S7-1500; and Rockwell CompactLogix 1756-L61 and 1756-L33ER. To ensure vendor-faithful compilation, deployment, and validation during fuzzing, we use each vendor’s default engineering software: RSLogix5000 for Rockwell, TIA Portal V14 for Siemens, and CODESYS 2.3 (Wago Automation Alliance) for WAGO.

Unless otherwise noted, all static analysis, seed generation, and fuzzing agents use `gpt-4o-2024-11-20` with temper-

ature 0 for determinism. To respect the query budget, we cap the seed-correction loop at five iterations. For coverage-guided parameter mutation, we set the UCB exploration coefficient to  $C = \sqrt{2}$  following Auer [3]. Each logic instruction is fuzzed for 12 CPU-hours.

### B. Real-world Bugs Discovered by LogicFuzz

LogicFuzz tested 338 logic instructions, generated 3,294 seed programs, and raised 514 alerts during fuzzing. Across static analysis, seed generation, and fuzzing, LLM queries cost \$146.31. Among the alerts, 147 were false positives: benign network-service responses (Modbug, TCP, DNP3, OPC) arrived after our preset alarm timeout and were misclassified as anomalies. We also observed 83 missed alarms because the anomaly detector failed to recognize the “Minor Fault” state string reported by RSLogix5000. After de-duplication and manual triage of the remaining 284 alerts, we confirmed 19 logic-instruction bugs across six PLCs, including four previously undisclosed vulnerabilities. We now analyze these bugs in detail.

As summarized in Table II, six bugs stem from missing boundary checks. For Rockwell, when LogicFuzz supplied wall-clock time (WCT) values corresponding to years 1900 and 9999 to GSV and SSV, RSLogix5000 reported a Minor Fault. Further analysis indicates that these instructions do not enforce appropriate upper/lower bounds on WCT inputs, causing faults on out-of-range yet syntactically valid parameters. An attacker can exploit such compliant-but-out-of-bounds parameters via the CIP protocol to trigger a denial-of-service (DoS) condition on the PLC. Likewise, SysMemMove, MemMove, SysMemCpy, and Memcpy accept overlapping or otherwise invalid pointers. Since the CODESYS manual does not clearly standardize the safety constraints of these instructions, LogicFuzz generated inputs that cause source and destination pointers to overlap, resulting in string overflows on two WAGO PLCs and leaking program/parameter addresses. On Siemens S7-1200 and S7-1500, MOVE\_BLK\_VARIANT and MOVE\_BLK invoke memcpy without validating source/destination positions; the ERROR LED turned red before clearing. Without bounds checks, these cases can corrupt PLC memory—potentially halting actuation or causing DoS if control logic is affected—and may access memory regions outside the PLC program’s execution sandbox, enabling information leakage.

Four defects in ALMD and ALMA arise from incorrect type handling. Both instructions default to treating label parameters as strings and interpret inputs  $-1$  and  $100$  as string lengths, leading to out-of-bounds accesses at addresses  $-1$  and  $100$ , respectively. The controller subsequently enters a Major Non-Recoverable Fault (MNRF)—halting operations, disabling outputs, and requiring manual recovery (e.g., firmware re-download) [44]. An attacker can leverage engineering-tool APIs to inject malicious payloads into the ALMA/ALMD parameters, making recovery costly and disrupting production.

We further identify a parameter-initialization flaw in MAJ. Although MergeSpeed and LockPosition are intended

to be constrained to  $\{0, 1\}$ , setting them to  $-1$  is not rejected by the engineering software; the PLC subsequently fails to process the value, leaving the controller suspended while the tool reports an unknown fault. Similarly, MRP fails to guard against integer overflow in its additive logic; overflowed results also suspend the PLC until restart, with RSLogix5000 reporting an unknown fault. Both issues enable a straightforward DoS vector.

Finally, SysMemSet, SysFileWrite, and SysFileRead do not validate target buffer pointers. For example, SysLibMemSet calls memset directly, and the file I/O routines only check `if (file)` without verifying buffer addresses. When LogicFuzz provided out-of-range pointers, WAGO PLCs crashed, disconnected from the engineering software, and showed a red RUN indicator. Such improper address/permissions handling risks unauthorized access to sensitive files or memory-resident secrets (e.g., PLC keys). Moreover, SysFileWrite allows writes to arbitrary paths outside the control program’s directory. Based on the operator manual indicating that WAGO PLCs run Linux, LogicFuzz generated test cases that attempt to write probe files and malicious payloads into root-protected directories; our monitor detected content changes in protected paths and classified this behavior as an unauthorized-access vulnerability. An attacker could exploit this primitive to persist malicious artifacts on the PLC and potentially escalate to full device compromise.

### C. Ablation Study

The ablation study quantifies the contribution of LogicFuzz’s five components—SDG generation (①), SDG mutation (②), candidate-program generation (③), program correction (④), and coverage-guided parameter mutation (⑤)—via five configurations. Cfg 1 removes SDG generation (①); downstream stages receive only the instruction name and a correct invocation relation. Cfg 2 removes SDG mutation (②) but retains the initial SDG. Cfg 3 removes our structured candidate-generation procedure (③) and replaces it with a single generic prompt (“Generate a test program for the instruction using an enable signal.”). Cfg 4 removes program correction (④). Cfg 5 removes coverage-guided mutation (⑤) and instead uses type-aware random parameters.

We evaluate each configuration using three metrics: (i) valid-seed ratio over the 338 instructions (counting both the seed program and its generated test cases), (ii) total alerts raised during fuzzing, and (iii) average coverage across the 338 programs. For each instruction, all six configurations (full + five ablations) terminate once the per-instruction LLM query budget of \$0.05 is exhausted.

As shown in Table III, removing SDG generation (Cfg 1) sharply reduces the valid-seed ratio to 61.63% (vs. 88.47% for the full system) and more than halves the number of alerts (63 vs. 142). This indicates that SDG-derived context (e.g., bug clues and parameter-usage constraints) is critical for synthesizing semantically valid, fuzzable seeds. Disabling SDG mutation (Cfg 2) further collapses alerts to 44—far

TABLE III: Ablation results for LOGICFUZZ’s five components.

| Configuration   | Valid Seed Ratio (%) | Alarms | Avg Coverage (%) |

|-----------------|----------------------|--------|------------------|

| Cfg 1 (②,③,④,⑤) | 61.63                | 63     | 16.43            |

| Cfg 2 (①,③,④,⑤) | 87.24                | 44     | 13.11            |

| Cfg 3 (①,②,④,⑤) | 31.52                | 8      | 16.83            |

| Cfg 4 (①,②,③,⑤) | 74.21                | 77     | 17.71            |

| Cfg 5 (①,②,③,④) | 86.17                | 36     | 9.37             |

| LogicFuzz       | 88.47                | 142    | 22.33            |

below the full system’s 142—suggesting that SDG mutation is a primary driver of “depth”, i.e., reaching behaviors that trigger non-trivial failures. Notably, the valid-seed ratio also drops (87.24% vs. 88.47%), consistent with the generator being confined to the initial SDG and less able to escape semantic/syntactic dead ends; iterating SDG mutation with validation allows LogicFuzz to explore alternative but semantically consistent instruction relations and recover valid seeds.

Replacing structured candidate generation (Cfg 3) yields the lowest valid-seed ratio (31.52%), underscoring the importance of the fixed, enable-signal-aligned template in producing compilable, executable programs. Removing program correction (Cfg 4) decreases the valid-seed ratio to 74.21% ( $\approx 14\%$  absolute below full). In the full system, 47 seeds required one correction round, 15 required two, and 9 required three; none required four or five. Thus, the five-iteration cap is conservative, and correction also improves cost efficiency: the average LLM cost per successful seed is \$0.038 (LogicFuzz) versus \$0.079 (Cfg 4). Finally, removing coverage-guided mutation (Cfg 5) keeps the valid-seed ratio relatively high (86.17%) but reduces alerts to 36 and drops average coverage to 9.37% (vs. 22.33% full), indicating that unguided parameter exploration substantially limits test depth.

Overall, SDG generation and SDG mutation are the main drivers of reach and bug-finding depth; the structured template and correction primarily improve seed validity and cost efficiency; and coverage-guided mutation is critical for broad, deep exploration as reflected by coverage and alert yield.

#### D. Comparison with Existing Work

To the best of our knowledge, LogicFuzz is the first framework purpose-built for fuzzing PLC logic instructions. Prior work overlaps with individual modules (e.g., seed synthesis or feedback collection) but does not provide an end-to-end pipeline for instruction-level fuzzing. Where applicable, we adapt and extend these techniques into component-wise baselines to enable fair comparisons and to isolate the impact of LogicFuzz’s design choices.

**Static analysis.** We compare LogicFuzz’s static analysis against the knowledge-retrieval agent in Agent4PLC [24], an LLM-based control program generator. LogicFuzz extracts invocation relationships via AST traversal, whereas Agent4PLC relies on LLM-only semantic extraction. For fairness, we augmented Agent4PLC’s retrieval prompt with: “Please extract the parameter dependencies, the calling relations, and execution

orders for the given logic instruction,” use its default retrieval context window (four 1K-character chunks), and provide both systems with the same manual. We then manually audit all 338 instructions. LogicFuzz recovers invocation relations for all 338 (100%), whereas Agent4PLC succeeds on 121. The gap is largely due to context truncation in Agent4PLC’s limited session window, which causes the LLM to omit required calls, hallucinate missing relations, and misorder execution steps.

Across the 1,743 bug clues attached to LogicFuzz’s SDGs, 98.71% fall into four categories: buffer overflows, out-of-bounds reads, integer overflows, and insufficient index validation. We attribute this distribution to two vendor-side tendencies: (i) emphasis on physical control logic that under-specifies finite bit-width constraints (e.g., overflow bounds and sign handling), and (ii) extensive use of raw pointers in internal services and communications without strict bounds enforcement, increasing the risk of out-of-bounds access and index/offset misuse.

**Seed program generation.** We evaluate seed generation capability by comparing LogicFuzz with Agent4PLC and PromptFuzz [25], adding the enable-signal mechanism to both baselines for fairness. For Agent4PLC, we rewrite the query as: “Generate a test program using the enable signal mechanism for the given logic instruction.” For PromptFuzz, we substitute logic-instruction manuals for APIs, replace “API” with “logic instruction” in its prompts, and append enable-signal logic to produce executable programs. To ensure consistent correctness criteria across vendors and methods, we evaluate all generated seeds using LogicFuzz’s unified correction, verification, and validation pipeline.

Each method generates one seed per instruction (338 total), and we measure the fraction that passes LogicFuzz’s validation. To reduce backend-specific variance, we also test two code-oriented LLMs (DeepSeek [16] and Claude [2]). We additionally report average generation time and the average number of repair iterations to capture end-to-end generation cost. As shown in Table IV, LogicFuzz achieves a substantially higher pass rate than both baselines, highlighting the benefit of instruction-oriented semantic constraints. PromptFuzz produces  $\approx 1\%$  valid programs; its 14 successes correspond to elementary arithmetic/Boolean operations that require little semantic extraction. Agent4PLC’s valid outputs similarly cluster in “light semantic, resource-independent” categories (arithmetic/logic, timers/counters, strings, type conversions), which do not require scan-cycle-aware state management and are well represented in pretraining corpora. For vendor-specific, resource-sensitive, and state-dependent instructions, even with enable-signal/ scan-cycle scaffolding, Agent4PLC often fails to reconstruct parameter dependencies and preconditions, and it frequently omits required pointer/handle initialization, reuse, or reset, yielding semantically invalid programs.

LogicFuzz also exhibits lower generation cost than Agent4PLC and PromptFuzz (9.10 seconds average generation time and 1.50 repair iterations), indicating that SDG-guided semantic constraints reduce invalid generations and unnecessary repair cycles. Table IV further shows clear backend

TABLE IV: Evaluation covers all 338 logic instructions. For each method, we report: (1) *Passed*/338 (pass rate), (2) *Time*/338 (average generation time), and (3) *Iters*/338 (average number of repair iterations). *Row Avg.* reports, for each model, the mean pass rate/time/iters across methods, while *Col. Avg.* aggregates each method across the three models.

| Model            | Agent4PLC |               |            | PromptFuzz |               |            | LogicFuzz |               |            | Row Avg.            |

|------------------|-----------|---------------|------------|------------|---------------|------------|-----------|---------------|------------|---------------------|

|                  | Pass (%)  | Avg. Time (s) | Avg. Iters | Pass (%)   | Avg. Time (s) | Avg. Iters | Pass (%)  | Avg. Time (s) | Avg. Iters |                     |

| GPT-4o           | 28.00%    | 14.72         | 2.21       | 0.89%      | 17.83         | 4.62       | 92.90%    | 7.32          | 1.44       | 40.60% / 13.29/2.76 |

| DeepSeek-R1      | 21.89%    | 20.38         | 2.37       | 2.07%      | 32.17         | 4.93       | 89.94%    | 10.87         | 1.57       | 37.97% / 21.14/2.96 |

| Claude Sonnet 4  | 25.15%    | 17.06         | 2.19       | 1.18%      | 24.09         | 4.71       | 91.98%    | 9.11          | 1.49       | 39.44% / 16.75/2.80 |

| <b>Col. Avg.</b> | 25.01%    | 17.39         | 2.26       | 1.38%      | 24.70         | 4.75       | 91.61%    | 9.10          | 1.50       | 39.34% / 17.06/2.84 |

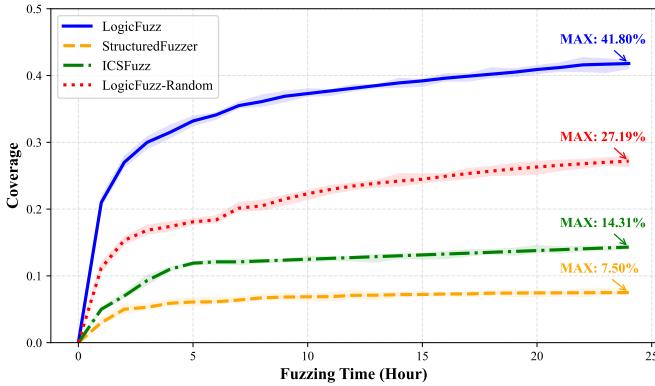

Fig. 12: Coverage comparison of LOGICFUZZ, StructuredFuzzer, and ICSFuzz over 24 hours. The solid line denotes mean coverage, and the shaded band indicates the min-max range.

differences: GPT-4o attains the highest average pass rate (40.60%), together with the lowest average time cost (13.29 seconds per program) and the fewest repair iterations (2.76 per program), motivating its use as our default backend.

**Mutation strategy.** To assess LogicFuzz’s mutation strategy, we compare it with ICSFuzz [40] and StructuredFuzzer [22], two recent control-program fuzzers that mutate instruction/function block parameters. These baselines represent different philosophies: StructuredFuzzer uses uninformed random value generation, whereas ICSFuzz prioritizes parameters whose mutations are associated with new path discovery. To fairly adapt them to logic-instruction fuzzing, we retain LogicFuzz’s static analysis, seed generation, and test-case construction, and replace only the coverage-guided parameter mutation policy with each baseline. Concretely, StructuredFuzzer becomes type-consistent random sampling; for ICSFuzz, we replace its “new path discovered” trigger with LogicFuzz’s “new memory block hit” condition derived from memory-block coverage. We additionally disable bug-oriented parameter mutations and keep only random parameter mutations, forming LogicFuzz-Random to isolate the contribution of LLM/SDG-guided semantic mutations.

We run 24-hour campaigns for each of the 338 instructions and evaluate all methods using LogicFuzz’s coverage metric. As shown in Figure 12, LogicFuzz reaches high coverage sub-

TABLE V: Average per-test execution time (**T**) and average memory usage (**M**) by PLC and tool.

| PLC Model           | LogicFuzz |       | LogicFuzz-GUI |       | LogicFuzz-ICS |       | LogicFuzz-Quartz |       |

|---------------------|-----------|-------|---------------|-------|---------------|-------|------------------|-------|