# VDORAM: Towards a Random Access Machine with Both Public Verifiability and Distributed Obliviousness

Huayi Qi<sup>\*†</sup>, Minghui Xu<sup>\*✉</sup>, Xiaohua Jia<sup>‡</sup>, and Xiuzhen Cheng<sup>\*</sup>

<sup>\*</sup>School of Computer Science and Technology, Shandong University, Qingdao, Shandong, China

<sup>†</sup>Institute for Network Sciences and Cyberspace, Tsinghua University, Beijing, China

<sup>‡</sup>Department of Computer Science, City University of Hong Kong, Kowloon, Hong Kong SAR, China

Email: qi@huayi.email, mhxu@sdu.edu.cn, csjia@cityu.edu.hk, xzcheng@sdu.edu.cn

**Abstract**—Verifiable random access machines (vRAMs) serve as a foundational model for expressing complex computations with provable security guarantees, serving applications in areas such as secure electronic voting, financial auditing, and privacy-preserving smart contracts. However, no existing vRAM provides distributed obliviousness, a critical need in scenarios where multiple provers seek to prevent disclosure against both other provers and the verifiers, because existing solutions struggle with a paradigm mismatch between MPC and ZKP that limits the development of practical multi-prover ZKP front-ends. This gap arises because MPC protocols are optimized for minimal computation, whereas ZKPs require a complete trace for proving. Furthermore, adapting RAM designs is also challenging, as vRAMs are not built for the high costs of oblivious execution and existing DORAMs lack public verifiability.

To address these challenges, we introduce **CompatCircuit**, the first multi-prover ZKP front-end implementation to our knowledge, designed to bridge this gap. **CompatCircuit** integrates collaborative zkSNARKs with novel MPC protocols, unifying computation and verification into a single compatible circuit paradigm. Building upon **CompatCircuit**, we present **VDORAM**, the first publicly verifiable distributed oblivious RAM. **VDORAM** reconciles the high communication latency of online MPC with the complexity of offline proof generation, resulting in a RAM design that balances these competing demands. We have implemented **CompatCircuit** and **VDORAM** in approximately 15,000 lines of code, demonstrating their practical feasibility through extensive experiments, including micro-benchmarks, comparative analysis, and program examples.

## I. INTRODUCTION

Random access machines (RAMs) serve as a crucial model for expressing complex computational logic, especially in the field of secure computation. A RAM executes a program on its processor (register-based [11], [3], [78], [13], [51], [31], [56] or stack-based [58], [57], [25]) with a random access

<sup>✉</sup> Minghui Xu is the corresponding author (Email: mhxu@sdu.edu.cn).

TABLE I

COMPARISON OF RANDOM ACCESS MACHINE SCHEMES.

|                                        | Verifiable to participants or designated verifiers | Publicly verifiable                                |

|----------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Non-oblivious                          | vRAM [46]                                          | vRAMs<br>[57], [58], [25]<br>[78], [21], [61]      |

| Oblivious with non-distributed secrets | vRAMs<br>[26], [38], [37], [39], [76]              | vRAMs<br>[11], [13], [77], [3]<br>[19], [31], [29] |

| Oblivious with distributed secrets     | DORAMs<br>[48], [74], [51], [44], [23]             | This work:<br><b>VDORAM</b>                        |

memory<sup>1</sup>. Table I summarizes our classification of RAMs based on obliviousness and verifiability:

*Verifiable random access machine (vRAM).* A vRAM enables a prover to execute a RAM program on an input and generate a proof of correct execution. *Verifiability:* vRAMs relying on private-coin interactive zero-knowledge proofs (ZKPs) offer verifiability exclusively to designated verifiers [46], [26], [38], [37], [39], [76]. In contrast, vRAMs based on non-interactive zero-knowledge (NIZK) proofs achieve public verifiability, producing proofs that can be verified by any entity, either with a privacy consideration [11], [13], [77], [3], [19], [31], [29] or without it [57], [58], [25], [78], [21], [61]. Some publicly verifiable vRAM schemes with succinctness are also known as zero-knowledge virtual machines (zkVMs) [3], [61] or zero-knowledge Ethereum virtual machines (zkEVMs) [58], [57], [25]. Succinctness means the proof size and verification complexity sub-linear in the size of the statement, i.e., the verification time is much less than the proof generation time. Consequently, succinct vRAMs often act as layer-2 scaling solutions for blockchain smart contracts. *Obliviousness:* Non-oblivious vRAMs, although most of them are based on ZKPs, prioritize performance [21], [61], [78] or compatibility [57],

<sup>1</sup>In this paper, the abbreviation “RAM” consistently refers to random access machines. Because the major challenge in a RAM involves implementing and checking random access memory, a proportion of related literatures may refer to “RAM” as random access memory.

[58], [25] by compromising on privacy. Conversely, other vRAMs inherently exhibit obliviousness due to the zero-knowledge property, either with public verifiability [11], [13], [77], [3], [19], [31], [29] or without it [26], [38], [37], [39], [76], ensuring that no information about the prover’s secret inputs is leaked to verifiers beyond what can be inferred from the output. However, a significant constraint of oblivious vRAMs lies in the fact that the prover, being a single entity, is required to possess knowledge of all the secrets. This requirement restricts their use in scenarios where secrets are distributed among multiple provers.

*Distributed oblivious random access machine (DORAM):* In DORAMs, a group of parties collaboratively execute a RAM program, each exclusively holding partial inputs, without relying on a central trusted entity knowing all secrets. Distributed obliviousness ensures that no information is leaked to any party during program execution, except for the revealed output. DORAMs are generally built upon multi-party computation (MPC) techniques. Semi-honest DORAMs [63], [56] lack verifiability, while maliciously secure DORAMs [48], [51], [23] inherently achieves verifiability within the parties, which is different from public verifiability.

To the best of our knowledge, no existing RAM schemes simultaneously offer both public verifiability and distributed obliviousness. Such a RAM would be valuable in scenarios where verifiers cannot trust any of the provers [66], [2], while each prover seeks to prevent the disclosure of their secrets against other parties or verifiers. We therefore pose the following question:

*Can we construct a publicly verifiable distributed oblivious RAM (VDORAM)?*

At first glance, this appears to be an engineering challenge of integrating two known technologies, an MPC system and a multi-prover ZKP system like collaborative zkSNARKs [66]. However, a deeper investigation reveals a fundamental conflict between the design philosophies of MPC protocols and multi-prover ZKP. We detail these challenges along with our contributions in response.

**There is a fundamental paradigm mismatch between MPC and ZKP, which has hindered the emergence of a practical multi-prover ZKP front-end.** The goal of an MPC protocol is minimalist secure computation; its design is optimized to reduce communication and processing overhead by computing a final result from minimal information. In contrast, the goal of a ZKP system is verifiability. It demands a complete and static trace of the entire computation, where every single intermediate value must serve as a witness within a constraint system. While this integration is straightforward for basic arithmetic like addition and multiplication [47], the paradigm mismatch is particularly evident for more sophisticated functionalities such as comparisons, equality checks, and bit-wise operations. The MPC protocols for these tasks often rely on procedures that do not generate the complete set of auxiliary witnesses required to construct a valid and non-trivial ZKP constraint. This mismatch makes a simple integration of existing tools unworkable. For instance, a state-of-the-art MPC

comparison protocol [64] determines a result by extracting only the most significant bit (MSB) of a difference, which is highly efficient for computation. However, this shortcut is incompatible with ZKP systems, as MSB-based approach does not hold on a finite field  $\mathbb{F}_p$ , where a ZKP system works on, and the single output bit is insufficient evidence to prove the comparison was performed correctly. Therefore, the mismatch has been a primary obstacle preventing the emergence of practical, programmable front-ends for multi-prover ZKPs. Consequently, prior works have had to either assume such a tool exists [66] or resort to proving randomly generated, non-programmable relationships [62], [40].

**Contribution.** Our work provides **CompatCircuit**, a multi-prover ZKP front-end that establishes a new MPC-for-ZKP paradigm. Instead of treating MPC and ZKP as incompatible systems, **CompatCircuit** unifies secure computation and proof generation into a single, compatible circuit paradigm. We identified core functionalities from single-prover front-ends [41], [52] and re-engineered them for the multi-prover context. This resulted in two new fundamental primitives beyond standard arithmetic: a modified inversion-or-zero protocol that safely handles zero inputs, and a full bit-decomposition protocol extracting *all* bits of a field element, fulfilling a strict ZKP requirement that existing MPC tools like MPyC and MP-SPDZ do not meet. Because the underlying primitives are designed to be both secure and provable, any gadget built from them automatically inherits these guarantees. Therefore we build a rich library of higher-level gadgets, such as comparisons, conditional selections, and equality checks, which are created through direct composition. By building on these primitives and gadgets, **CompatCircuit** allows developers to construct complex multi-prover ZKP applications with a familiar circuit-design experience, effectively brings an MPC-for-ZKP paradigm.

**How to make the random access machine execution simultaneously oblivious and publicly verifiable.** The entire state transition of the machine, including memory access, must be performed blindly among the provers, yet this blind execution must produce a trace that can be proven correct in a ZKP. Conventional vRAMs are unsuitable because their witness generation is a plaintext execution, which is fundamentally non-oblivious. They optimize under the assumption that this plaintext execution is computationally free. Conversely, existing DORAMs are designed for obliviousness but not for public verifiability. DORAMs seek to minimize communication and computation overheads in oblivious operations, with a focus on optimizing oblivious data structures [50], such as oblivious arrays [48], [51] and oblivious caches [23] to facilitate efficient access across distributed secrets, without considering the requirements of publicly verifiable proof generation.

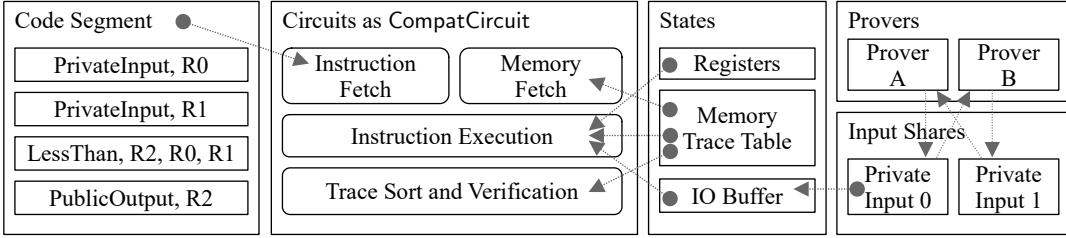

**Contribution.** In response, we build VDORAM on top of our **CompatCircuit** system, the main architecture demonstrated in Figure 1. VDORAM is a register-based random access machine that allows an arbitrary number of provers to blindly execute a program on their distributed secret inputs. The machine state, including the program counter and register

Fig. 1. VDORAM architecture.

values, remains secret-shared throughout the execution. To prevent side-channel leakage, the execution time is constant regardless of the instruction type being processed, ensuring that the operational pattern reveals no information. In the end of the execution, a publicly verifiable proof can be generated to prove the validity of execution to external verifiers who does not trust any of the provers. A central component of VDORAM is its memory management scheme, which is architecturally designed to balance the inverted performance costs of this new paradigm. It reconciles the high communication latency of the online MPC computation with the complexity of offline proof generation. This leads to a design that strategically makes trade-off between these competing demands, resulting in a functional system despite the inherent overheads of its stronger security model. We also make VDORAM open-source at <https://github.com/BDS-SDU/vdoram-artifacts/> and demonstrate the capabilities of VDORAM with 7 program examples, micro-benchmarks, and comparasion with prior works.

Our contributions are summarized as follows:

- 1) We introduce **CompatCircuit**, the first front-end framework, to our knowledge, for multi-prover ZKP applications that introduces the MPC-for-ZKP paradigm by unifying secure computation and proof generation into a single, compatible circuit.

- 2) We design and construct VDORAM, the first random access machine that achieves both public verifiability and distributed obliviousness.

- 3) We provide a full, open-source implementation of our **CompatCircuit** and VDORAM system and conduct a comprehensive evaluation, demonstrating the practical feasibility of the VDORAM model.

**Roadmaps.** Section II introduces related works. Section III details the model and preliminaries. In Section IV, we present our VDORAM design, including the **CompatCircuit** framework, memory management, the full protocol, and analysis. The implementation and evaluation are presented in Section V. Section VI concludes our work and discusses possible future directions.

## II. RELATED WORK

This section presents a review of related work, including both succinct and non-succinct verifiable RAMs. Furthermore, it encompasses distributed oblivious RAMs.

**Succinct vRAMs.** Ben-Sasson et al. proposed the first SNARK-based verifiable RAM, TinyRAM [11], in which the

execution proof can be formulated as a zkSNARK arithmetic circuit. Subsequently, vnTinyRAM [13] was introduced, which provides universality, making it independent of the specific program being executed. These efforts enable subsequent research in the field.

Several vRAMs prioritize compatibility with the Ethereum Virtual Machine (EVM), aiming to support smart contract rollups for blockchain layer-2 solutions. These vRAMs include Polygon zkEVM [58], zkSync [57], and Scroll [25]. Since the EVM inherently lacks support for private variables, these projects generally favor succinctness over the zero-knowledge property. In contrast, Polygon Miden [59] strives to be an EVM-incompatible vRAM that caters to privacy concerns within the blockchain space, at the expense of EVM compatibility.

Other notable succinct vRAMs include Cairo [33], which presents a verifiable RAM rendered in zkSTARK, utilizing an algebraic intermediate representation (AIR) rather than an arithmetic circuit/R1CS, coupled with a write-once memory model. Risc0 [77] is another STARK-based vRAM supporting the RV32IM ISA. Additionally, there are vRAMs with WebAssembly (WASM) support [30]. Recently, Arun et al. designed a RISC-V-based vRAM called Jolt [3], which increases efficiency by implementing lookup singularity: all circuits solely perform lookups into pre-computed tables.

**Non-succinct vRAMs.** Some vRAMs sacrifice succinctness to achieve significantly better proof generation times. In contrast to employing zk-SNARKs, these vRAMs construct their proofs utilizing non-succinct zero-knowledge proof techniques such as MPC-in-the-Head [42], ZK from vector oblivious linear evaluation (VOLE) [20], [6], [75], and ZK from garbled circuits [43]. In this context, proof schemes operating under the private coin setting are inherently interactive, necessitating verifier participation in the proof generation process. Conversely, schemes reliant on public coins can be made non-interactive by employing the Fiat-Shamir transformation [24], thereby preserving public verifiability.

Heath et al. developed a ZK oblivious RAM, termed BubbleRAM [37], where the zero-knowledge proof is constructed using garbled schemes [43]. Subsequently, BubbleCache [39] was introduced, which enhanced efficiency through the implementation of multi-level caching. Franzese et al. built a constant-overhead interactive verifiable RAM [26], improving memory checking efficiency using a polynomial equality check. Goel et al. [31] developed their implementation, named

Dora, based on the proposed concept of ZKBag. By introducing disjunctive zero-knowledge [6], [32], [53], [54], [55], their approach further enhances efficiency by allowing introducing additional instructions to the processor circuit at no extra cost. Saint Guilhem et al. proposed the construction of verifiable RAM based on public-coin ZKPs [19].

**Distributed Oblivious RAMs.** Differing from vRAMs that focus on public verifiability, distributed oblivious random access machines (DORAMs) [73] represent a significant area in a multi-party setting, which is also known as RAM-MPC. Here, each party holds a portion of the secret and they work together to execute the RAM without relying on a trusted entity to hold all the secrets. Marcel Keller introduced a practical implementation of an oblivious machine within the arithmetic black-box model [48], leveraging SPDZ [18], an MPC protocol that offers active security. Subsequently, Keller et al. devised a garbled-circuit-based RAM with active security [51], which minimizes the number of broadcast rounds between memory accesses. Ji et al. [44] concentrated on constructing a RAM capable of private function evaluation. Falk et al. have introduced a 3-party distributed RAM-MPC framework [23] that boasts logarithmic overhead and is resilient to malicious adversaries. In addition, Hamlin et al. proposed their first construction of FHE-based ORAM [36], [35].

Numerous efforts have been directed toward implementing RAM with a focus on either public verifiability or distributed obliviousness. However, research remains sparse in scenarios where both properties are of significance. The existence of a VDORAM, verifiable distributed oblivious random access machine, is a question that has not been comprehensively addressed.

### III. MODEL AND PRELIMINARIES

This section begins with an introduction to our model, including system roles, threat model, and the essential properties of our VDORAM. Subsequently, we will introduce several underlying building blocks, including collaborative zkSNARKs, multi-party computation, arithmetic circuits, and RAM runtimes.

#### A. System and Threat Model

Our VDORAM is designed to create a distributed oblivious vRAM that enables a group of provers to collaboratively execute a given program using their individual inputs. Upon completion, the provers collectively convince non-interactive verifiers, attesting to the integrity of the outputs.

The following are the system roles along with the associated threat model.

- *Provers.* Provers are responsible for operating the VDORAM runtime, supplying input data, and generating zero-knowledge proofs for verifiers. *Correctness:* The group of provers is considered malicious to verifiers: it is assumed that 0 provers will act honestly, i.e., all provers are eager to collude to compromise the correctness of results for their personal gains. *Privacy:* Provers do not seek privacy if they are able to compromise correctness. If it's

nearly impossible to compromise correctness, the provers attempt to protect their secrets from being exposed: each prover is considered as a polynomial time adversary, curious to obtain confidential information from other provers, where at least  $t$  (e.g.,  $t = 1$ ) provers will act honestly to protect their secrets from being exposed.

- *Non-interactive verifiers.* Similar to participants in traditional NIZK contexts, verifiers in our system can be any entity that assesses the validity of the proofs provided by the provers. These verifiers are not entrusted with any confidential or sensitive data, except for that which can be inferred from the public outputs.

- *Trusted initializer.* They generate the public parameters for collaborative zkSNARKs, as well as precomputed data such as beaver triples for MPC.

- *Program vendors.* They publicly provide programs to be executed within the VDORAM runtime. These programs are audited and are trusted not to embed additional information in their outputs.

Our VDORAM necessitates the following properties.

- *Completeness.* Honest provers can complete the computation process and generate a valid proof.

- *Knowledge soundness.* Even in the event of collusion among all provers to produce a false proof, the probability of successfully passing the verification process remains negligible.

- *Succinctness.* The verification time should be significantly less than the computation and proof generation time.

- *Zero-knowledge.* Verifiers should not acquire any confidential information from any prover, except for those derived from public output.

- *Distributed obliviousness.* Each prover should not acquire any confidential information from any other prover, except for those derived from public output and private output meant to be revealed among provers.

The provers firstly utilize an MPC protocol for computing all necessary intermediate values as secret shares. Subsequently, they apply collaborative zkSNARKs [66] to generate a publicly verifiable proof using these secret shares as witnesses. We adopt a dishonest-majority MPC protocol supporting mixed boolean logic and arithmetic computations over a finite field  $\mathbb{F}_p$  and the ring  $\mathbb{Z}_{2^n}$ . Below explains the considerations:

- *Integrating zkSNARKs.* Our threat model assumes that the entire set of provers may be malicious. While a maliciously secure dishonest-majority MPC protocol guarantees the privacy of computations as long as at least  $t$  provers behave honestly, we additionally require public verifiability. This is achieved by enabling independent verification of the computations' correctness through collaborative zkSNARKs. This approach ensures that even if all provers collude, a public verifier can still verify the integrity of the computation.

- *Mixed computations.* Collaborative zkSNARKs typically operate on statements expressed as arithmetic operations over a finite field  $\mathbb{F}_p$ . However, unlike a standalone MPC

application, when MPC is used to support zkSNARKs, it must compute auxiliary data in addition to the primary computational result. This necessitates supporting computations in both the boolean domain and the ring  $\mathbb{Z}_{2^n}$ . This mixed-domain computation is essential for generating the necessary inputs for the zkSNARK proof system.

## B. Preliminaries

1) *Collaborative zkSNARKs*: A zero-knowledge Succinct Non-interactive ARgument of Knowledge (zkSNARK) is a cryptographic protocol in which a prover  $\mathcal{P}$  convinces a verifier  $\mathcal{V}$  that a pair  $(x, w) \in R$  without revealing  $w$ . Here,  $x$  is referred to as the instance or public input, and  $w$  serves as the private input, also known as the witness. Initially, zkSNARKs [34], [65], [28], [15] were designed for a single prover  $\mathcal{P}$ . Then, Ozdemir et al. expanded this scheme to a multi-prover scenario, introducing the concept of collaborative zkSNARKs [66]. This concept were further improved in [62], [2], [40]. In a collaborative zkSNARK,  $m$  provers  $\mathcal{P}_0, \mathcal{P}_1, \dots, \mathcal{P}_{m-1}$  each hold a witness  $w_i$  and they collectively aim to convince the verifier  $\mathcal{V}$  that  $(x, w_0, w_1, \dots, w_{m-1}) \in R$ . This protocol contains the following algorithms:

- $\text{Setup}(1^\lambda, R) \rightarrow \text{pp}$ : Produces the public parameters pp.

- $\text{Prove}(\text{pp}, x, w_0, w_1, \dots, w_{m-1}) \rightarrow \pi$ : Generates a proof  $\pi$  if  $(x, w_0, w_1, \dots, w_{m-1}) \in R$  in MPC; aborts otherwise.

- $\text{Verify}(\text{pp}, x, \pi) \rightarrow \{0, 1\}$ : Validates the proof  $\pi$ .

An  $(m, t)$  collaborative zkSNARK has properties as follows:

- *Completeness*: Honest provers generate a valid proof when they have valid witnesses such that  $(x, w_0, w_1, \dots, w_{m-1}) \in R$ .

- *Knowledge soundness*: Provers without knowledge of valid witnesses cannot produce a valid proof.

- *t-zero-knowledge*: If less than  $t$  provers collude, provers and verifiers cannot gain any information about witnesses  $w_0, w_1, \dots, w_{m-1}$  (excluding  $w_i$  for prover  $\mathcal{P}_i$ ).

- *Succinctness*: Both the proof size and the verification time are  $o(|R|)$ , where  $|R|$  denotes the size of relation  $R$ .

2) *Multi-Party Computation*: A multi-party computation (MPC) protocol [18], [10], [49] involves  $m$  parties, each performing computations to determine the outcome  $y \leftarrow f(x_0, x_1, \dots, x_{m-1})$ , where  $f$  is a function defined as  $f : X^m \rightarrow Y$ . In this protocol, each party  $i$  possesses an input  $x_i \in X$ . An MPC protocol is considered secure if it reveals no additional information beyond that which is implicit in the output  $y$ . As long as no more than  $t$  parties collude, the protocol maintains its security.

In particular, our research focuses exclusively on dishonest-majority MPC protocols. In *dishonest-majority* MPC protocols, where typically  $t = m - 1$ , additive secret sharing is utilized. In this scheme, a secret value  $a$  is distributed among the parties as  $a_0, a_1, \dots, a_{m-1}$ , each party holding a share such that the sum of all shares equals  $a$ . We use the notation  $[a]$  to denote the secret shares of the value  $a$  held by each party. To compute addition  $r \leftarrow a + b$ , each party computes their share as  $[r] \leftarrow [a] + [b]$  within ring or fields. To compute multiplication  $r \leftarrow a \cdot b$ , parties consume a pre-shared Beaver

triple  $([\alpha], [\beta], [\gamma])$  such that  $\alpha \cdot \beta = \gamma$ . They broadcast and reveal  $\delta$  and  $\epsilon$  where  $[\delta] = [a] - [\alpha]$  and  $[\epsilon] = [b] - [\beta]$ . The final share is computed as  $[r] \leftarrow [\gamma] + \delta \cdot [\beta] + \epsilon \cdot [\alpha] + \delta \cdot \epsilon$ .

To facilitate complex operations beyond simple arithmetic, particularly those requiring bit-level manipulation within a prime field setting, we additionally utilize two techniques in mixed MPC: doubly-authenticated bit (**daBit**) [70] and extended doubly-authenticated bits (**edaBit**) [22]. A **daBit** consists of a random bit  $r \in [0, 1]$  that is secret-shared among parties in both an arithmetic domain  $[r]_p \in \mathbb{F}_p$  and a Boolean domain  $[r]_2 \in [0, 1]$ , useful to convert a Boolean secret share into an arithmetic share by utilizing B2A<sub>p</sub> protocol [1]. Similarly, an **edaBit** provide shares of a random value  $r \in \mathbb{F}_p$  in an arithmetic domain  $[r]_p \in \mathbb{F}_p$ , along with shares of its individual bits  $[r]_i \in [0, 1]$  ( $i \in [0, l]$ , where  $l$  denotes the bit length of  $p$ ) in a Boolean domain.

Publicly verifiable MPC, also known as publicly auditable MPC, is usually constructed by committing values to a public bulletin-board and constructing an NIZK proof checking the transcript [5], [7], [8], [69], [47]. Alternatively, Ozdemir et al. [66] proposed a novel publicly verifiable MPC construction from their proposed multi-prover ZKP, verifying statements in R1CS. We favor this latter approach due to its capability to enable the construction of efficient proofs focused on only checking the integrity of RAM states, as opposed to validating the entire sequence of computations leading to those states.

3) *Arithmetic Circuit*: An arithmetic circuit [13], [67], [14], [9] is a directed acyclic graph (DAG) consisting of gates and wires, commonly used in both MPC and zkSNARKs programming. Each wire carries a value within a finite field  $\mathbb{F}_p$ ; additionally, they may also operate within a ring  $\mathbb{Z}_{2^n}$  for MPC, which we will utilize later. Gates in the circuit take in wires as inputs and generate output wires based on the operation they perform, either addition or multiplication. Moreover, arithmetic circuits can be easily converted to rank-1 constraint system (R1CS).

4) *Rank-1 Constraint System*: An R1CS is a set of constraints, where each constraint is a triplet of vectors  $\mathbf{a}, \mathbf{b}, \mathbf{c}$  satisfying  $(\mathbf{a} \cdot \mathbf{s}) \cdot (\mathbf{b} \cdot \mathbf{s}) - \mathbf{c} \cdot \mathbf{s} = 0$  in  $\mathbb{F}_p$ . Here,  $\mathbf{s}$  is the solution vector, which contains instances (all constant or public inputs) and witnesses (all private inputs and all intermediate values). This structure forces any complex computation to be flattened into a series of additions and multiplications checks, which is typically done by a ZKP front-end.

5) *Verifiable Random Access Machine*: We adopt the definition from [3] and [30]. A random access machine runtime is defined as a program receiving an input tuple  $(\mathbf{I}, E, \text{in})$ , where  $\mathbf{I}$  denotes a code image vector of instructions,  $E$  represents the entry point, and  $\text{in}$  denotes input data.

A register-based RAM maintains a state  $s$ , represented by the tuple  $(\text{pc}, \mathbf{R}, \mathcal{M}, \text{halt})$ , where  $\text{pc}$  denotes the program counter, referring the location of an instruction in the code image vector  $\mathbf{I}$ ,  $\mathbf{R}$  represents a set of registers that hold values,  $\mathcal{M}$  denotes the memory state, and  $\text{halt}$  is a public bit indicating whether the machine has reached its termination. The RAM runtime simulates the semantics of each instruction

and produces execution states. Each execution state  $s_i$  is generated from the previous state  $s_{i-1}$  by executing the related instruction. The execution of the RAM runtime is considered *valid* when each new state follows the expected result from the prior state, with all states except the last one remaining non-halted. A verifiable RAM consists of the following procedures:

- $\text{Setup}(1^\lambda, \mathbf{I}, E) \rightarrow \text{pp}$ : Generates public parameters.

- $\text{Compute}(\mathbf{I}, E, \text{in}) \rightarrow \text{out}, \mathbf{s}$  : Computes output  $\text{out}$  with each machine state  $s_i$  by simulating the RAM runtime.

- $\text{Prove}(\text{pp}, \mathbf{I}, E, \text{in}, \text{out}, \mathbf{s}) \rightarrow \pi$  : Generates an execution proof  $\pi$ ; aborts if state transitions are invalid.

- $\text{Verify}(\text{pp}, \mathbf{I}, E, \text{in}, \text{out}, \pi) \rightarrow \{0, 1\}$ : Verifies the proof  $\pi$  on whether state transitions are valid.

#### IV. VDORAM: PUBLICLY VERIFIABLE DISTRIBUTED OBLIVIOUS RAM

We favor advocate for the development of VDORAM from a publicly verifiable MPC through leveraging multi-prover ZKPs, due to its capability to enable the construction of succinct proofs focused on only checking the integrity of RAM states, as opposed to validating the entire sequence of computations leading to those states. We present the overview of the VDORAM in Section IV-A, achieving publicly verifiable MPC with multi-prover ZKPs. Subsequently, in Section IV-B, we discuss our *CompatCircuit* framework. This framework provides an MPC-for-zkSNARK construction, facilitating the integration of commonly utilized MPC functionalities for a multi-prover vRAM. Following that, in Section IV-C, we explore a memory management scheme tailored for a multi-prover environment, making a trade-off between communication overhead in computation stage and the circuit size that determines the proof generation overhead. Finally, we outline our VDORAM protocol in Section IV-D and provide analysis in Section IV-E.

##### A. Overview

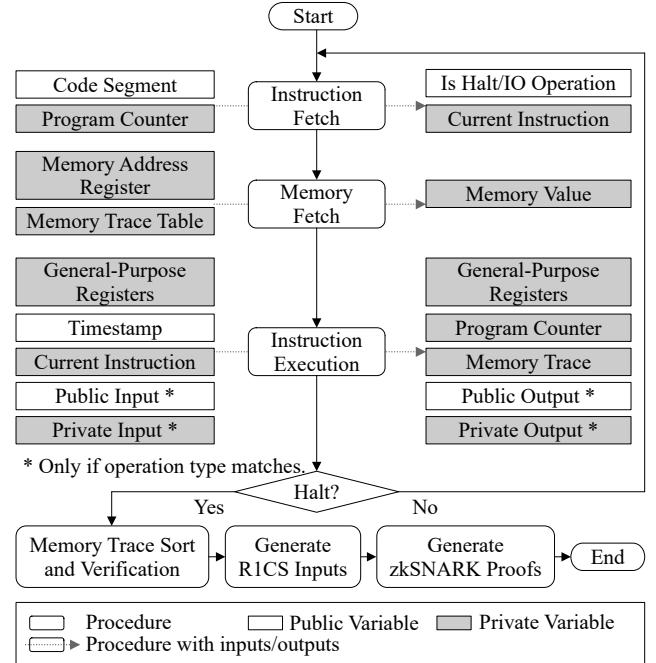

The overall workflow of VDORAM is shown in Figure 2. A publicly provided program is represented as a code segment containing multiple instructions. Provers, who exclusively hold secret inputs, collaboratively execute the machine and produces a proof by executing instruction fetch, memory fetch, instruction execution, trace sort and verification circuits.

At a high level, we can implement VDORAM from adapting traditional single-prover vRAMs [13], [58], where only necessary verifications are involved to check the integrity of RAM states. This adaptation involves several modifications: migrating the plaintext front-end computation to an MPC-based oblivious computation, committing to hash digests of public values, and associating the results of oblivious computation with R1CS witnesses. The workflow is shown in Figure 2. During each iteration, the provers commence by covertly retrieving the instruction to be executed, based on a blind program counter. Concurrently, they discretely fetch the possible memory value that may be required during the instruction execution. If the instruction does not entail a memory operation, a dummy memory value is still fetched from

Fig. 2. Workflow of VDORAM.

the memory trace table. Following this, the provers execute the instruction by updating registers, interacting with I/O, and generating memory access operations, without knowing the specific nature of the instruction being executed. Even if there is no match, a dummy memory access is created and inserted into the memory trace table. These steps are repeated until the machine halts. Subsequently, the provers demonstrate the integrity of the memory accesses through a consistency check.

However, at a detailed level, we still face challenges, including the limited availability of sophisticated publicly verifiable MPC protocols, the lack of front-end implementations for multi-prover ZKPs, and the unsuitability or inefficiency of existing random access memory designs for computations requiring both distributed obliviousness and public verifiability. We will address these challenges in Section IV-B and Section IV-C.

##### B. *CompatCircuit*: A Unified Front-End for Multi-Prover Computation and Multi-Prover Proofs

We introduce *CompatCircuit*, a front-end for multi-prover ZKPs that systematically adapts MPC protocols for generating R1CS witnesses. Our approach eliminates dependencies on plaintext values common in single-prover front-ends by replacing conditional branching with oblivious computations, such as using an inversion-based zero test for equality checks instead of relying on knowing the condition's validity [19]. We also redesign MPC protocols unsuitable for ZKPs; for instance, where an efficient MPC comparison [64] is insufficient for ZKP statement construction, we substitute it with a sequence of boolean operations on decomposed bits. To this end, we improved the bit-decomposition protocol from [17], that supports extract *all* bits from a finite field  $\mathbb{F}_p$ , overcoming the

limitations of existing MPC libraries [71], [49] which do not extract all bits required for ZKP. Furthermore, **CompatCircuit** acts as a compatibility layer to unify the MPC and ZKP codebases, providing a familiar development environment akin to single-prover ZKP tools and thereby minimizing implementation complexity and human error.

We propose our **CompatCircuit** as four primitives and gadgets. Primitives include field addition, multiplication, inversion-or-zero, and fully bit-decomposition. The protocols for inversion-or-zero, and fully bit-decomposition are shown in Figure 3. We then extend other commonly used functionalities provided in existing single-prover zkSNARK toolchains, particularly *circcomlib* [41] and *jsnark\_interface* [52], as the composition of the four primitives, namely gadgets.

### Protocol $\Pi_{\text{InvOrZero}}$

**Input:** A secret-shared field value  $[a]$ .

**Protocol:**

- 1) Compute  $[r] \leftarrow [a]^{p-2}$  with  $\lceil \log_2 p \rceil$  multiplications.

- 2) Compute witnesses for R1CS constraints  $a \cdot (a \cdot r - 1) = 0$  and  $r \cdot (a \cdot r - 1) = 0$ .

### Protocol $\Pi_{\text{FBits}}$

**Input:** A secret-shared field value  $[a]$ ,  $l$  daBits, an edaBit ( $[b] \in \mathbb{F}_p$ ,  $[b_0], [b_1], \dots, [b_{l-1}] \in \{0, 1\}$ ) providing secret shares of a random field value with its bits [22].

**Protocol:**

- 1) Compute  $[c] \leftarrow [a] - [b] \in \mathbb{F}_p$ , and reveal  $c \in \mathbb{F}_p$ . Then, compute plaintext value  $d \leftarrow c + 2^l - p \in \mathbb{Z}_{2^{l+1}}$ , and perform plaintext bit-decomposition on  $d$ , getting bits  $(d_0, d_1, \dots, d_{l-1}, d_l)$ .

- 2) Use a bit adder with carry up to add bit sequence  $([b_0], [b_1], \dots, [b_{l-1}])$  with  $(d_0, d_1, \dots, d_{l-1}, d_l)$ . Denote the result bit sequence as  $([e_0], [e_1], \dots, [e_l])$ .

- 3) Denote the most-significant bit  $[e_l]$  as  $[q] \in \{0, 1\}$ . Denote  $(p_0, p_1, \dots, p_{l-1})$  as the bit sequence of field prime  $p \in \mathbb{Z}_{2^l}$ . Multiply each public bit with  $[1 - q]$ , getting  $([f_0], [f_1], \dots, [f_{l-1}])$ .

- 4) Use a bit adder with carry up to add bit sequence  $([e_0], [e_1], \dots, [e_{l-1}])$  with  $([f_0], [f_1], \dots, [f_{l-1}])$ . Denote the results  $([a'_0], [a'_1], \dots, [a'_{l-1}])$ .

- 5) For each boolean share  $[a'_i] \in \{0, 1\}$  ( $i \in [0, l-1]$ ), convert it back to arithmetic share  $[r_i] \in \mathbb{F}_p$  by consuming a daBit, using B2A<sub>p</sub> protocol proposed in Prio+ [1].

- 6) Compute witnesses for R1CS constraints  $a = \sum_{i=0}^{l-1} r_i \cdot 2^i$  and  $(r_0, r_1, \dots, r_{l-1}) < (p_0, p_1, \dots, p_{l-1})$ .

Fig. 3. The protocols for inversion-or-zero and full bit-decomposition in **CompatCircuit**. The inversion-or-zero protocol generalizes the input domain to include zero while preserving privacy over whether the input is zero. The full bit-decomposition protocol ensures all bits of the input are extracted in their arithmetic shares, enabling the satisfaction of R1CS constraints.

*Inversion-or-zero:* Inspired by [41], we introduce this primitive to facilitate an efficient construction of equality checks. In this protocol, each participant holds an arithmetic additive secret share  $[a]$  of a field element  $a \in \mathbb{F}_p$ . The inversion-or-zero operation will produce  $r \leftarrow 0$  if and only if  $a = 0$ . Otherwise, it outputs the inverse  $r \leftarrow a^{-1}$ , ensuring that  $a \cdot a^{-1} = 1$ . Importantly, information regarding whether  $a = 0$  remains confidential. The typical efficient constant-round MPC construction, which depends on  $a \neq 0$  and is facilitated by disclosing the product of  $a$  with a random multiplier, is unsuitable due to this confidentiality requirement. Instead, the MPC implementation harnesses Fermat's little theorem to compute the inverse, necessitating  $\lceil \log_2 p \rceil$  multiplications. Additionally, adjustments are made to the R1CS statements. Ordinarily, one R1CS statement  $a \cdot r = 1$  suffices, as it presupposes  $a \neq 0$  in typical field inversions. However, to maintain correctness under our modified conditions, we employ four multiplications, ensuring the simultaneous validity of two statements:  $a \cdot (a \cdot r - 1) = 0$  and  $r \cdot (a \cdot r - 1) = 0$ .

*Fully bit-decomposition:* We construct a fully bit-decomposition protocol that extracts all bits from a field element, building upon and enhancing the efficiency of a prior MPC implementation [17] since other constructions [49], [71] do not apply. Initially, each participant holds an arithmetic additive secret share  $[a]$  of a field element  $a \in \mathbb{F}_p$ . This bit-decomposition operation results in  $l = \lceil \log_2 p \rceil$  bits, denoted as  $r_i$  ( $i \in [0, l-1]$ ), such that the equation  $a = \sum_{i=0}^{l-1} r_i \cdot 2^i$  is satisfied. Subsequently, each participant receives an arithmetic additive secret share, denoted as  $[r_i]$ , for each bit  $b_i$  ( $i \in [0, l-1]$ ). In the original implementation by [17], an additional bit  $[q]$ , indicating whether an overflow occurs, is computed from a separate comparison of two bit sequences, and  $p$  is subtracted only if  $[q]$  is true. Our construction circumvents this comparison by consistently subtracting  $p$  during the first bit addition. Consequently,  $[q]$  naturally emerges as the most significant bit of the result. The original conditional subtraction has been replaced by a conditional addition executed only when  $[1 - q]$  is true. This adjustment enhances the efficiency of the protocol. We refer to the full version of our paper [68] for the correctness.

We now construct other commonly used functionalities [41], [52] as the composition of the four primitives. Boolean logic and if-else selection can be directly represented using field addition and multiplication, zero test and equality check requires an inversion-or-zero operation, while less-than comparison require bit-decompositions.

- *Boolean logic.* Although operations should primarily handle field elements in  $\mathbb{F}_p$  as inputs and outputs, it is also feasible to simulate boolean AND/OR/XOR/NOT operations with field additions and multiplications, assuming the input field element is in range  $\{0, 1\}$ .

- *If-else selection.* This operation selects a value  $a$  if condition bit  $c$  is true, or  $b$  otherwise. This is usually implemented as  $r \leftarrow a \cdot c + b \cdot (1 - c)$ .

- *Zero test.* This maps a field element to a boolean value indicative of whether it is zero. Given an element  $a$ ,

return  $b = 1$  if  $a = 0$ , otherwise return 0. This can be implemented using the inversion-or-zero primitive: let  $\text{inv}$  represent the inversion-or-zero result of  $a$ , and then return  $b \leftarrow 1 - a \cdot \text{inv}$ .

- *Equality check.* To avoid conditionally branching introduced in [19], we migrate the implementation by [41], which begins by subtracting the two elements and subsequently zero-testing the difference.

- *Less-than comparison.* Given two elements  $a$  and  $b$ , return a bit  $c$  indicating whether  $a < b$ . It is constructed from initially performing fully bit-decomposition of the two elements and subsequently comparing them utilizing boolean operations. The bit sequences and intermediate results act as auxiliary witnesses to prove the correctness. Despite its higher complexity compared to a pure MPC implementation [64], the increased overhead is justified by the proof requirements.

With **CompatCircuit**, it becomes straightforward to construct the execution circuit for VDORAM. We refer to the full version of our paper [68] for the protocols of all VDORAM circuits. However, it remains to be determined whether the memory fetch, trace sort, and trace verification circuits can achieve efficient construction in obliviousness. This will be the focus of our investigation in the following subsection.

### C. Memory Management: Balancing Oblivious Computation Overheads with Proof Generation Complexity

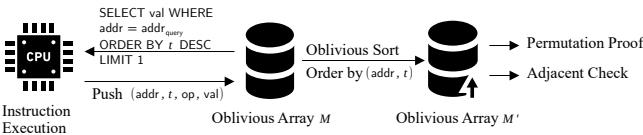

Fig. 4. Memory management scheme of VDORAM.

As shown in Figure 4, we construct a multi-prover memory management scheme based on [26]. The main procedures are as below: 1) During each instruction execution, a memory access tuple  $m = (\text{addr}, t, \text{op}, \text{val})$  is generated and saved to the oblivious array  $M$ , where  $t$  refers to a monotonically increasing timestamp and  $\text{op}$  indicates if the memory access is a load or a store instruction. Note that in our VDORAM, we also want to hide whether the instruction relates to memory access or not, and therefore, if not, we specify the memory address  $\text{addr}$  with the maximum value,  $p - 1$  in  $\mathbb{F}_p$ . 2) During each memory fetch, the stored memory value might be obliviously fetched with an address filter, and if there are multiple values, select the one with the largest  $t$ , which means the most recent value that corresponds to the address. 3) After the machine halts, the prover needs to prove the correctness of  $T$  memory accesses. First, sort the vector  $M'$  from  $M$  so that  $M'$  is ordered firstly by memory address  $\text{addr}$ , then by time  $t$ . Then, a permutation check enforces that no values are altered during the sorting process. Following this, a memory consistency check scans the sorted vector, and for each pair of adjacent lines  $i$  and  $i + 1$ , the following condition from [26]

holds, ensuring that for each load operation, the value retrieved matches the most recently stored value at that address:

$$\begin{aligned} & ((\text{addr}_i < \text{addr}_{i+1}) \vee ((\text{addr}_i = \text{addr}_{i+1}) \wedge (t_i < t_{i+1}))) \\ & \wedge ((\text{addr}_i \neq \text{addr}_{i+1}) \vee (\text{val}_i = \text{val}_{i+1}) \vee (\text{op}_{i+1} = \text{store})) \\ & \wedge ((\text{addr}_i = \text{addr}_{i+1}) \vee (\text{op}_{i+1} = \text{store})) \end{aligned} \quad (1)$$

Now, we will discuss detailed construction in a multi-prover setting. By incorporating **CompatCircuit**, we can program this verification statement within **CompatCircuit**, facilitating the automatic construction of MPC protocol to compute and provide the necessary secret-shared auxiliary inputs for collaborative zkSNARKs. However, there are more considerations beyond a naive combination.

**Oblivious array.** Single-prover vRAMs employ a plaintext array to manage memory data. Transitioning to a multi-prover context, we can replace the plaintext array with an oblivious storage element similar to those utilized in MPC-based DORAM schemes. For instance, a 2-party Circuit ORAM [73] used by [48], or a 3-party random access memory [23].

In VDORAM, the oblivious storage is required to facilitate the confidential insertion or overwriting of new memory values at a specified address, retrieving the latest memory value corresponding to that address, and supporting memory consistency checks. We demonstrate the ideal functionality needed by our VDORAM in Figure 5, where the auxiliary data  $\text{aux} = (t, \text{op})$ . Note that, our VDORAM requires a unique  $\mathcal{F}_{\text{HistoricalKV}}.\text{Export}()$  functionality, which is not needed for a regular DORAM.

### Functionality $\mathcal{F}_{\text{HistoricalKV}}$

**Parameters.** Memory size  $n$  that restricts the address  $\text{addr} \in [0, n - 1]$ .

**Functionality.**  $\mathcal{F}_{\text{HistoricalKV}}.\text{Add}(\text{addr}, \text{val}, \text{aux})$ : add or update memory value  $\text{val}$  associated with address  $\text{addr}$ .  $\mathcal{F}_{\text{HistoricalKV}}.\text{Query}(\text{addr})$ : return the latest memory value  $\text{val}$  associated with address  $\text{addr}$ .  $\mathcal{F}_{\text{HistoricalKV}}.\text{Export}()$ : return an oblivious array containing all  $(\text{addr}, \text{val}, \text{aux})$  tuples, including those being overwritten.

Fig. 5. Ideal functionality for the memory storage in VDORAM.

The implementation of  $\mathcal{F}_{\text{HistoricalKV}}$  should maintain obliviousness, meaning provers must not acquire any supplementary information about any given  $\text{addr}$ . For instance, provers should even remain unaware of the number of times an *unknown* memory address has been accessed, as disclosing such information could compromise security. A conventional DORAM scheme commences by initializing the storage and then simulating memory accesses online, *overwriting* the storage if the address already contains a value. This approach of discarding outdated data is appropriate for traditional DORAM implementations, which do not require public verifiability since integrity can be evaluated based on the security guaranteed by maliciously secure MPC. To enable public verifiability, it

is critical to retain all historical memory accesses from which the proof is derived.

One initial approach involves implementing  $\mathcal{F}_{\text{HistoricalKV}}$  by adapting the oblivious storage employed in DORAM, along with an append-only oblivious array to store  $(\text{addr}, \text{val}, \text{aux})$  for each  $\mathcal{F}_{\text{HistoricalKV}}.\text{Add}()$  access. Nevertheless, despite the requirement for provers to allocate approximately double the space for two oblivious structures, existing efficient DORAM schemes support an insubstantial number of parties. This does not align with our VDORAM aims, which seek to accommodate an arbitrary number of provers beyond just two or three. Consequently, we have implemented this functionality in MPC using only one linearly-scanned oblivious array, with an additional requirement that the timestamp  $t$  contained in  $\text{aux}$  *must* exhibit a monotonically increasing pattern every time  $\mathcal{F}_{\text{HistoricalKV}}.\text{Add}()$  is invoked. Protocol  $\Pi_{\text{HistoricalKV}}$ :

- Upon receiving  $\Pi_{\text{HistoricalKV}}.\text{Add}(\text{addr}, \text{val}, \text{aux})$ , insert the tuple to the end of array  $M$ .

- Upon receiving  $\Pi_{\text{HistoricalKV}}.\text{Query}(\text{addr})$ , for each memory tuple  $m_i$  in array  $M$ , compute  $b_i \leftarrow \text{EqualityCheck}(\text{addr}, \text{addr}_i) \in \{0, 1\}$ . Then, set  $b_i \leftarrow 0$  if there exists a larger  $b_j = 1$  where  $j > i$ . Finally, return  $\sum_{i=1}^{|M|} b_i \cdot \text{val}_i$ .

- Upon receiving  $\Pi_{\text{HistoricalKV}}.\text{Export}()$ , return the array  $M$ .

**Oblivious sort.** Migrating vRAM into multi-prover setting, the vector  $M$  is no longer in plaintext. We must sort the vector in a manner that conceals its values. This is a problem well-studied in the literature [4] [45]. We opted for Bitonic mergesort; however, adapting this algorithm for VDORAM necessitates modifications. Initially, the scheme from [26] requires an ordered vector  $M'$  primarily by memory address  $\text{addr}$ , and secondly by time  $t$ . Typically, this is achieved by performing a stable sorting by time, followed by a second sorting by address. However, since Bitonic mergesort is inherently unstable, we introduce a complex comparer, slightly increasing overhead by adding an additional equality check:  $m_1 < m_2 \iff (\text{addr}_1 < \text{addr}_2) \vee ((\text{addr}_1 = \text{addr}_2) \wedge (t_1 < t_2))$ . Moreover, Bitonic mergesort requires the size of vector  $|M|$  to be a power of 2. Hence, we must pad the vector before sorting and subsequently remove the padded elements post-sorting without plaintext access. We append the vector with padding item  $m_{\text{pad}} = (p-1, p-1, p-1, p-1)$ , where  $p-1 \in \mathbb{F}_p$ . These padding items, being greater than any real memory access tuples, allow provers to safely remove them from the end of the vector without exposing the actual contents.

**Different consideration in memory check performance.** In single-prover vRAM, memory check schemes such as in [19] are generally considered more efficient than [26], featuring reduced proof generation time. However, the efficiency and associated overhead of a scheme differ significantly within our VDORAM context as opposed to a single-prover vRAM. In a conventional single-prover scenario, the computation stage where plaintext computations occur is essentially negligible and considered almost *free* in comparison to the complexity of the circuit verifying the statements. In [26], the memory access

vector  $M$  of size  $T$  is sorted, accompanied by a permutation proof and  $T-1$  less-than checks on adjacent timestamp values. Conversely, [19] expands the vector to size  $2T$ , implementing a permutation proof and  $T-1$  difference checks on adjacent timestamp values. In the single-prover scenario, [19] offers enhanced efficiency over [26], as sorting the values in plaintext is inexpensive, irrespective of whether the vector size is  $T$  or  $2T$ . However, operations such as the heavyweight less-than or lightweight difference checks must be represented within an arithmetic circuit, and the size of this circuit constitutes the primary overhead in proof generation. In contrast, multi-prover scenarios replace all plaintext values with secret shares in MPC, making latency a crucial factor. Computation stage is no longer free in terms of cost: an MPC sorting network incurs substantial overhead due to the extensive communication required. We will further demonstrate this overhead in our evaluation, Section V. Given these considerations, for our multi-prover implementation, we support the adoption of the memory checking protocol proposed in [26] in contrast to [19], due to its relative simplicity and reduced computational and communicational demands in multi-prover contexts.

#### D. Protocol Specification

Putting it all together, we construct our VDORAM, providing the full protocol below.

##### Protocol $\Pi_{\text{VDORAM}}$

**Input:** An instruction vector  $\mathbf{I}$  with entrypoint  $E$  is publicly provided.  $m$  provers exclusively and privately holds  $N$  inputs  $\text{in}_i$  which corresponds to the  $i$ -th input the machine asks for.

##### Protocol:

- 1) Trusted setup: the trusted initializer generates public parameters for collaborative zkSNARKs. Provers generate sufficient beaver triples,  $\text{edaBit}$ , and  $\text{daBit}$  for multi-party computation.

- 2) Each prover construct and broadcast secret shares of his/her input  $[\text{in}_i]$  to one other provers.

- 3) Set public timestamp  $t \leftarrow 0$ . Initialize all registers  $[R_j] \leftarrow 0$ . Set the program counter to the entrypoint  $[\text{pc}] \leftarrow E$ . Initialize memory access vector  $[\mathbf{M}] \leftarrow ()$ .

- 4) Provers run *instruction fetch* protocol. Given  $\mathbf{I}$  and  $[\text{pc}]$  as input, provers fetches the next instruction  $[I]$  as well as the instruction type indicator  $\text{op}_{\text{masked}} \in \{\text{input}, \text{output}, \text{secret}\}$ . This protocol does not reveal information about an non-IO instruction.

- 5) If  $\text{op}_{\text{masked}} = \text{input}$ , provers assign the input value  $[\text{in}] \leftarrow [\text{in}_i]$  where  $i$  denotes the count of previously provided inputs. Otherwise, provers publicly set it to 0.

- 6) If  $t \geq 1$ , provers run *memory fetch* protocol. Given  $[I]$ ,  $[R_{\text{addr}}]$ , and  $[\mathbf{M}]$ , provers fetches the latest memory value  $[\text{val}]$ . Private output  $[\text{val}]$  would be a secret-shared 0 if the instruction is not related with

memory access or the address has never been stored with a value. In particular, if  $t = 0$ , provers publicly sets  $[\text{val}] \leftarrow 0$ .

- 7) Provers run *instruction execution* protocol. Given  $[I]$ ,  $[\text{val}]$ ,  $t$ ,  $[\text{pc}]$ ,  $[\text{in}]$ , and all registers  $[R_j]$ , the protocol returns updated register values as  $[\text{pc}]'$  and  $[R_j]'$ . A memory access trace  $[m] = ([\text{addr}], t, [\text{op}], [\text{val}])$  is also produced. The protocol also returns the output value  $[\text{out}]$  if the operation type matches; otherwise, it's 0. Provers accordingly updates values and insert  $[m]$  to vector  $[\mathbf{M}]$ .

- 8) If  $\text{op}_{\text{masked}} \neq \text{halt}$ , increase  $t \leftarrow t + 1$  and go to the *instruction fetch* protocol.

- 9) Provers run *trace sort* protocol to pad and sort the memory access vector  $[\mathbf{M}]$ . Get sorted vector  $[\mathbf{M}]'$ .

- 10) Provers run *trace verification* protocol with input  $[\mathbf{M}]$  and  $[\mathbf{M}]'$ . The verification result is publicly revealed.

- 11) For all *instruction fetch*, *instruction execution*, and the final *trace verification* protocol, provers invoke collaborative zkSNARKs, providing all inputs, outputs, intermediate results, and auxiliary data with necessary hash digests, and getting an non-interactive succinct proof  $\pi$ .

During each round, provers begin by retrieving the next instruction to be executed through an *instruction fetch* circuit. Except for the case of a halt or IO operation, provers get no extra information about which instruction will be executed next. Subsequently, regardless of whether the instruction involves a memory read/write operation, they fetch the memory value for a specified address from a blind memory trace table using a *memory fetch* circuit. Following this, the *instruction execution* circuit is utilized to interpret the execution by computing, updating registers, inserting a new row to the memory trace table, and interacting with public/private I/O if the instruction type matches. These three types of circuits are repeatedly executed upon fetching an instruction, continuing until the machine reaches a halt state. Upon completion, the *trace sort* circuit is run to blindly pad and sort the memory trace table. This is succeeded by the execution of a *trace verification* circuit, which checks the correctness of the entire memory management process.

## E. Performance and Security Analysis

1) *Communication overhead of CompatCircuit primitives*: Let  $l = \lceil \log_2 p \rceil$  denote the number of bits in the finite field  $\mathbb{F}_p$ . An addition operation does not require communication, while a multiplication operation requires broadcasting one revealed element, thus incurring 1 round of communication. The inversion-or-zero operation necessitates  $l + 4$  rounds of multiplications:  $l$  multiplications to secretly obtain the inverse, and an additional 4 multiplications for constructing the verification statements. A fully bit-decomposition operation incurs  $19l + 2$  rounds of communications:

- 1 round for exposing  $c$ .

- $3l$  multiplications for an  $l$ -bit MPC adder with a plaintext operand, where each adder requires at most  $3l$  multiplications.

- $6l$  multiplications:  $l$  for multiplying each bit  $p_i$  with  $[1 - q]$ ,  $5l$  multiplications for an  $l$ -bit MPC adder with a secret operand.

- 1 round: exposing  $l$  boolean values for B2A <sub>$p$</sub>  protocol [1].

- $10l$  multiplications for computing R1CS witnesses:  $l$  for input range check,  $l$  for constructing the field element from input bits,  $8l$  for ensuring the bits are smaller than the bit decomposition of field modulus  $p$ .

### 2) *Communication overhead in the VDORAM protocol*:

In this analysis, we consider  $l$ , the number of bits in the finite field to be a small constant. We additionally denote  $T$  as the total number of iterations,  $N$  as the number of inputs, and  $I$  as the length of the instruction vector. It's worth noting that our VDORAM protocol employs a read-write memory model with a full address space, implying that the memory capacity is virtually unlimited (with a capacity of  $p$ ). Therefore, the overhead is not affected by the size of the memory. The VDORAM protocol incurs the following communication overheads:

- $m \cdot N$  broadcasts are required for distributing the secret shares of the inputs.

- $O(T \cdot I)$  rounds of communication occur during  $T$  invocations of the instruction fetch protocol. During each fetch, a linear scan is conducted to determine the next instruction to be executed, taking  $O(I)$  time.

- $O(T^2)$  rounds of communication are required for  $T$  instances of the memory fetch protocol. During each fetch, a linear scan is carried out to identify the most recent memory value to be read, taking  $O(T)$  time.

- $O(T)$  rounds of communication take place for  $T$  instances of the instruction execution protocol. The overhead from the instruction execution circuit can be considered a constant number of CompatCircuit primitives, as the number of registers and instruction types are small constants..

- $O(T \log^2 T)$  rounds are needed for the memory trace sorting protocol. The sorting algorithm requires  $O(T \log^2 T)$  comparisons, each necessitating a small constant number of bit-decomposition primitives.

- $O(T)$  rounds are required for the memory trace verification protocol. This protocol checks each pair of adjacent lines, which also involves comparisons based on bit-decomposition.

3) *Privacy Disclosure*: Our protocol  $\Pi_{\text{VDORAM}}$  is designed to maintain the confidentiality of sensitive information against both provers and verifiers. This includes:

- Register values: The contents of the registers are kept private, including the program counter  $\text{pc}$ .

- Memory accesses: Information about memory value, address, and access type is concealed. The number of memory accesses equals to the total number of instruction cycles.

**Definition IV.1.** An  $(m, t)$  VDORAM with  $m$  provers  $\mathbf{P} = \mathcal{P}_0, \mathcal{P}_1, \dots, \mathcal{P}_{m-1}$  holding public input  $\text{in}_{\text{pub}}$  and secret shares of private input  $\text{in}_{\text{priv}}$  is a RAM  $(\mathbf{I}, E, \text{in}_{\text{pub}}, \text{in}_{\text{priv}})$  with the following procedures:

- $\text{Setup}(1^\lambda, \mathbf{I}, E) \rightarrow \text{pp}$ : Generates zkSNARK parameters.

- $\text{Compute}(\mathbf{I}, E, \text{in}_{\text{pub}}, \text{in}_{\text{priv}}) \rightarrow \text{out}_{\text{pub}}, \text{out}_{\text{priv}}, \mathbf{s}$ : Computes  $\text{out}_{\text{pub}}$ ,  $\text{out}_{\text{priv}}$  with each machine state  $s_i$  by simulating the RAM runtime.

- $\text{Prove}(\text{pp}, \mathbf{I}, E, \text{in}_{\text{pub}}, \text{out}_{\text{pub}}, \text{in}_{\text{priv}}, \text{out}_{\text{priv}}, \mathbf{s}) \rightarrow \pi$  : Generates an execution proof  $\pi$ ; aborts if state transitions are invalid.

- $\text{Verify}(\text{pp}, \mathbf{I}, E, \text{in}_{\text{pub}}, \text{out}_{\text{pub}}, \pi) \rightarrow \{0, 1\}$ : Verifies the proof  $\pi$  on whether state transitions are valid.

and with the following properties:

- *Completeness*: For all  $(\mathbf{I}, E, \text{in}_{\text{pub}}, \text{in}_{\text{priv}})$ , the following statement holds:

$$\Pr \left[ \text{Verify}^H(\text{pp}, \mathbf{I}, E, \text{in}_{\text{pub}}, \text{out}_{\text{pub}}, \pi) = 1 \middle| \begin{array}{l} H \leftarrow \mathcal{U}(\lambda) \\ \text{pp} \leftarrow \text{Setup}^H(1^\lambda, \mathbf{I}, E) \\ \text{out}_{\text{pub}}, \text{out}_{\text{priv}}, \mathbf{s} \leftarrow \text{Compute}^H(\mathbf{I}, E, \text{in}_{\text{pub}}, \text{in}_{\text{priv}}) \\ \pi \leftarrow \text{Prove}^H(\text{pp}, \mathbf{I}, E, \text{in}_{\text{pub}}, \text{out}_{\text{pub}}, \text{in}_{\text{priv}}, \text{out}_{\text{priv}}, \mathbf{s}) \end{array} \right] \leq \text{negl}(\lambda)$$

- *Knowledge soundness*: For all  $(\mathbf{I}, E, \text{in}_{\text{pub}}, \text{in}_{\text{priv}})$  and for all sets of efficient algorithms  $\mathbf{P} = \mathcal{P}_0^*, \mathcal{P}_1^*, \dots, \mathcal{P}_{m-1}^*$ , there exists an efficient extractor  $\text{Ext}^{H, \mathbf{P}^H}$  such that:

$$\Pr \left[ (\mathbf{I}, E, \text{in}_{\text{pub}}, \text{out}_{\text{pub}}, \text{in}_{\text{priv}}, \text{out}_{\text{priv}}, \mathbf{s}) \in R \middle| \begin{array}{l} H \leftarrow \mathcal{U}(\lambda) \\ \text{pp} \leftarrow \text{Setup}^H(1^\lambda, \mathbf{I}, E) \\ \text{in}_{\text{priv}}, \text{out}_{\text{pub}}, \text{out}_{\text{priv}}, \mathbf{s} \leftarrow \text{Ext}^{H, \mathbf{P}^H}(\text{pp}, \mathbf{I}, E, \text{in}_{\text{pub}}) \end{array} \right] \geq \Pr \left[ \text{Verify}^H(\text{pp}, \mathbf{I}, E, \text{in}_{\text{pub}}, \text{out}_{\text{pub}}, \pi) = 1 \middle| \begin{array}{l} H \leftarrow \mathcal{U}(\lambda) \\ \text{pp} \leftarrow \text{Setup}^H(1^\lambda, \mathbf{I}, E) \\ \text{out}_{\text{pub}}, \pi \leftarrow \mathbf{P}^H(\mathbf{I}, E, \text{in}_{\text{pub}}) \end{array} \right] - \text{negl}(\lambda)$$

$R$  denotes the collection of valid RAM executions.  $\text{Ext}^{H, \mathbf{P}^H}$  denotes Ext has oracle access to  $H$  and may re-run the provers  $\mathbf{P}$  for multiple times with  $H$  re-programmed.

- *Succinctness*: Proof size and verification time are  $O(|\pi|)$ .

- *Zero-knowledge*: For all efficient  $\mathcal{A}$  controlling  $k \leq t$  provers  $\mathcal{P}_0, \mathcal{P}_1, \dots, \mathcal{P}_{k-1}$ , there exists an efficient simulator  $\text{Sim}$  such that for all  $(\mathbf{I}, E, \text{in}_{\text{pub}}, \text{in}_{\text{priv}})$  and for all efficient distinguishers  $D$ ,  $|D_0 - D_1| \leq \text{negl}(\lambda)$  holds, where:

$$D_0 = \Pr \left[ D^{H[\mu]}(\text{tr}) = 1 \middle| \begin{array}{l} H \leftarrow \mathcal{U}(\lambda) \\ \text{pp} \leftarrow \text{Setup}^H(1^\lambda, \mathbf{I}, E) \\ b \in \{0, 1\} = 1 \iff (\mathbf{I}, E, \text{in}_{\text{pub}}, \text{out}_{\text{pub}}, \text{in}_{\text{priv}}, \text{out}_{\text{priv}}, \mathbf{s}) \in R \\ (\text{tr}, \mu) \leftarrow \text{Sim}^H(\text{pp}, \mathbf{I}, E, \text{in}_{\text{pub}}, \text{out}_{\text{pub}}, (\text{in}_{\text{priv}}, \text{out}_{\text{priv}}, \mathbf{s})_{0,1,\dots,k-1}, b) \end{array} \right]$$

$$D_1 = \Pr \left[ D^H(\text{tr}) = 1 \middle| \begin{array}{l} H \leftarrow \mathcal{U}(\lambda) \\ \text{pp} \leftarrow \text{Setup}^H(1^\lambda, \mathbf{I}, E) \\ \text{tr} \leftarrow \text{View}_{\mathcal{A}}^H(\mathbf{I}, E, \text{in}_{\text{pub}}, \text{in}_{\text{priv}}, \text{out}_{\text{pub}}, \text{out}_{\text{priv}}, \mathbf{s}) \end{array} \right] \right]$$

$\text{tr}$  is a transcript,  $\text{View}_{\mathcal{A}}^H$  denotes view of  $\mathcal{A}$  when provers  $\mathcal{P}$  interact with  $\mathbf{I}, E, \text{in}_{\text{pub}}, \text{in}_{\text{priv}}, \text{out}_{\text{pub}}, \text{out}_{\text{priv}}, \mathbf{s}$  in Compute and Prove procedures,  $\mu$  is a partial function from  $H$  such that given an input  $x$ , function  $H[\mu]$  equals  $\mu(x)$  if  $x$  is in the domain of  $\mu$ , otherwise equals  $H(x)$ .

- *t-distributed-obliviousness*: Conditions are same as Zero-knowledge, except that  $\text{out}_{\text{priv}}$  is visible among provers. So the definition is slightly different: update  $\text{out}_{\text{pub}} \leftarrow \text{out}_{\text{pub}} \cup \text{out}_{\text{priv}}$  and  $\text{out}_{\text{priv}} \leftarrow \emptyset$ .

• *Instructions*: The specific instruction being executed at any given time remains hidden, with some I/O exceptions. However,  $\Pi_{\text{VDORAM}}$  also requires some information to be publicly available. 1) I/O instruction type. Only `input`, `output`, and `halt` instructions are revealed to provers. Provers maintain the protocol, and thereby need to know when to provide input, when to expect output, and when the machine has completed its execution. *Mitigation*: For non-interactive programs, we can structure the program into three distinct

phases: input, computation, and output. During the input and output phases, data are simply transferred to and from registers/memory without any actual processing. This minimizes the risk of sensitive information being leaked through the public disclosure of I/O-related instruction types. 2) Total number of iterations ( $T$ ). Like most oblivious RAMs, the total number of instructions executed by the machine is made public. This is necessary to halt the machine and facilitate the proof generation process. *Mitigation*: Programmers should

design their code to minimize the impact of revealing the total iteration count. If the iteration count is directly related to a confidential value, introduce a dummy loop with a randomly determined number of iterations. If certain computational steps are optional based on the value of a confidential variable, include dummy loops to ensure a consistent iteration count regardless of the condition.

We now formally define VDORAM in Definition IV.1, adapting the frameworks from [66], [12].

**Theorem IV.1.** *If  $(\text{Setup}, \text{Prove}, \text{Verify})$  is an  $(m, t)$  collaborative zkSNARK, and  $\text{Compute}_{\text{MPC}}$  is an MPC protocol for  $\text{Compute}$  that is secure-with-abort against up to  $t$  corruptions, then a RAM  $(\mathbf{I}, E, \text{in}_{\text{pub}}, \text{in}_{\text{priv}})$  with procedures  $(\text{Setup}, \text{Compute}_{\text{MPC}}, \text{Prove}, \text{Verify})$  is an  $(m, t)$  VDORAM.*

Theorem IV.1 formally establishes the security properties of our VDORAM construction. The proof is provided in the full version of our paper [68].

## V. IMPLEMENTATION AND EVALUATION

In this section, we present the implementation of our proposed VDORAM along with the underlying **CompatCircuit**. We also design experiments to evaluate the various factors that influence performance.

**Implementation.** Our implementation consists of approximately 15,000 lines of C# code and additional components. Specifically, it includes the **CompatCircuit** library for unifying multi-party computation and R1CS verification with an MPC implementation ( $\approx 8,500$  lines), the VDORAM program ( $\approx 3,500$  lines), unit tests ( $\approx 2,500$  lines), evaluation programs and scripts ( $\approx 3,500$  lines), and modifications to the Rust program `collaborative-zksnark` [66] ( $\approx 300$  lines). Our source code is available at <https://github.com/BDS-SDU/vdoram-artifacts>. Figure 6 shows an example of designing a circuit in **CompatCircuit**. We refer to the full version of our paper [68] for VDORAM implementation details.

**Evaluation Setup.** Our experiments were conducted on a server instance on ESXi 8.0 virtualization platform with various hardware allocation. Denote the prover count as  $m$ , the server instance simulating multiple provers was allocated with up to  $4m$  vCPU cores from Intel Xeon 4214R @ 2.4 GHz, 16m GB of RAM, and 20m GB of disk space, running Debian Linux 12 as the operating system. Note that our implementation is *not* parallelized, but more than one CPU core is needed to handle the communication among other provers. The elliptic curve used in our experiment is BLS12-377, and the collaborative zkSNARKs variant employed is Plonk [28].

The variables altered in our experiments included: the number of MPC provers (2, 4, 8, and optionally 16), RAM program instruction types (multiplication, comparison, hashing, memory store, and memory load), and the number of instruction cycles (4, 16, 20, 32, 50, and 64). We recorded time costs throughout the entire process, including the phases of MPC preprocessing, computation, ZKP setup, proof generation, and verification associated with executing VDORAM.

```

public class DemoCircuit : ICircuitBoardGenerator {

public CircuitBoard GetCircuitBoard() {

CircuitBoard cb = new();

// Private inputs

Wire a = Wire.NewPrivateInputWire("a");

Wire b = Wire.NewPrivateInputWire("b");

cb.AddWires(a, b);

// Comparison gadget

GadgetInstance g = new FieldLessThanGadget()

.ApplyGadget([a, b], "a_lt_b");

g.Save(cb);

// Public output

g.OutputWires[0].Name = "out_lt";

g.OutputWires[0].IsPublicOutput = true;

return cb;

}

}

```

Fig. 6. An example of designing a circuit in **CompatCircuit**, our unified multi-prover ZKP front-end that unifies representation for secure computation and R1CS constraints.

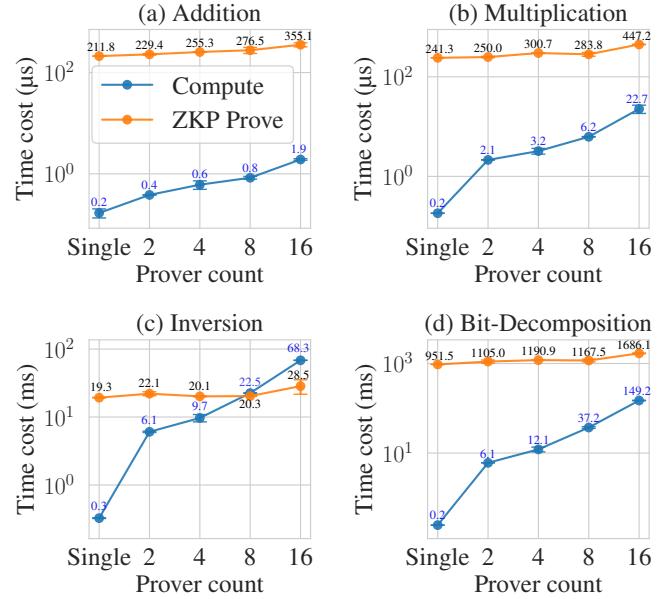

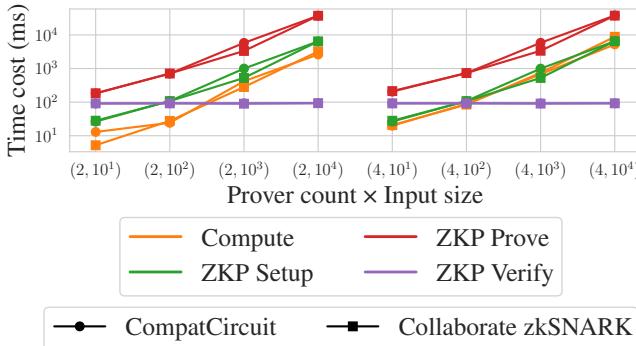

Fig. 7. Micro-benchmarks of **CompatCircuit** primitives.

**Micro-benchmarks of CompatCircuit.** We first evaluated the performance overhead in **CompatCircuit**, as shown in Figure 7. When compared with the single-prover baseline, the computation time costs for a 2-prover configuration increased by up to 20 times. This rise can be attributed to the transition from single-party to multi-party computation, which brings additional complexities such as sharing revealing in Beaver multiplications and the implementation of the bit-decomposition protocol. The overhead is indispensable as prover parties in a multi-prover setting cannot compute in the same manner as a single-prover scenario. Subsequently, the increase in computation time becomes less steep as the number

of provers grows. For instance, with an 8-prover setup, our system is capable of processing 1,250,000 additions, 150,000 multiplications, 45 inversions, or 25 bit-decompositions per second, which we consider to be a reasonable and acceptable performance outcome.

**Comparison of CompatCircuit.** To contextualize CompatCircuit’s capabilities, we compare it with prior multi-prover ZKP works, specifically Collaborative zkSNARKs [66], Liu et al. [62], and Hu et al. [40]. Table II summarizes the key differences among these systems.

TABLE II

COMPARISON OF COMPATCIRCUIT WITH PRIOR WORKS

| Multi-Prover System         | Primary Focus        | Computation Support                 |

|-----------------------------|----------------------|-------------------------------------|

| Collaborative zkSNARKs [66] | ZKP back-end         | Limited (hardcoded multiplications) |

| Liu et al. [62]             | Proof delegation     | No (proving random relationship)    |

| Hu et al. [40]              | Proof delegation     | No (proving random relationship)    |

| <b>CompatCircuit (ours)</b> | <b>ZKP front-end</b> | Yes                                 |

We experimentally compared CompatCircuit with Collaborative zkSNARK using a benchmark of  $n$ -th sequential squaring ( $v \leftarrow v^2$ ), as this is the only hardcoded computation that Collaborative zkSNARK supports natively without a front-end. Figure 8 illustrates the time costs for different procedures with varying numbers of provers and input sizes. The results demonstrate that both systems exhibit comparable performance, indicating that CompatCircuit achieves its additional features without significant performance penalties.

Fig. 8. Performance comparison between CompatCircuit and Collaborative zkSNARK. In this figure, the compute procedure also contains preprocessing time costs.

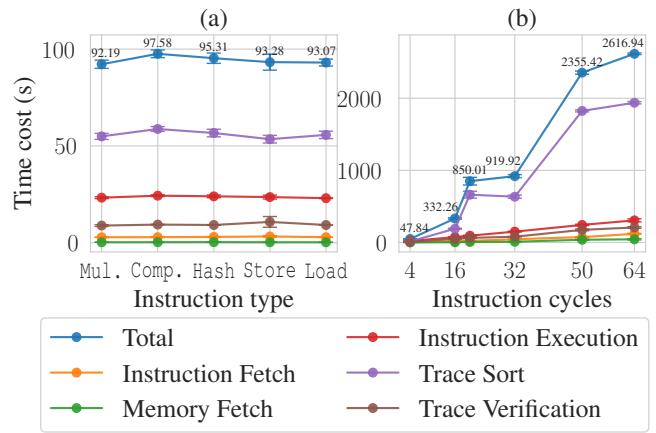

**Micro-benchmarks of VDORAM.** We subsequently assessed the performance of the VDORAM within an 8-prover configuration, as shown in Figure 9. We varied both the types and counts of instructions. In Figure 9(a), we set the instruction cycle count to 5, with varying instruction types. We observed that the execution time remains constant, regardless of the instruction type. This observation can be explained by the privacy demand, where everything *might* happen *must* happen, to prevent any chance of information leakage through the operation types used.

Fig. 9. Computation time costs of VDORAM (8 provers) with (a) varying instruction types and (b) varying instruction cycles. Time costs remain constant with different types but increase with instruction cycles.

In Figure 9(b), the instruction cycle count varied from 4 to 64. We observed that the time costs associated with instruction fetch, memory fetch, instruction execution, and trace verification circuits are roughly constant per instruction (i.e., linear to the instruction cycle count). However, the time cost for the trace sort circuit increases significantly when the instruction cycle count reaches a power of two. This increase is expected because, in MPC, we used the Bionic mergesort algorithm which has an  $O(T \log^2 T)$  time complexity in sequential computation and requires padding the items to a power of two. The trace sort circuit consumes a considerable amount of time in the computation stage. Fortunately, this circuit acts as an MPC-only CompatCircuit which does not require verification and can be further optimized by paralleling the computation.

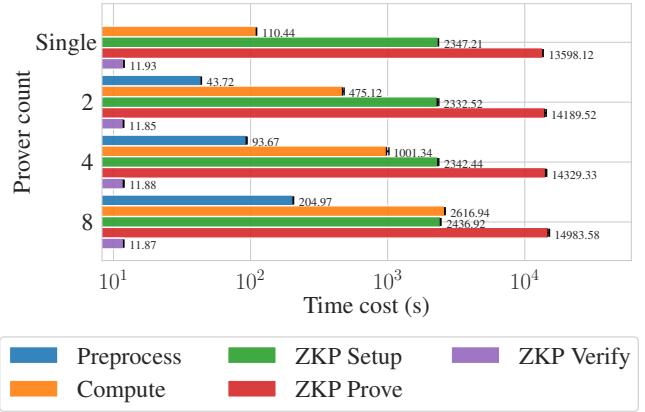

Fig. 10. Time costs of VDORAM procedures (instruction cycles: 64).

Lastly, we present the overall performance results across varying prover counts, using a single-prover setup as the baseline. The time costs are shown in Figure 10. We also estimated the bandwidth requirements during the computation and collaborative ZKP process: for communicating with

each of the other  $m - 1$  prover parties, the highest average bandwidth for an individual prover was 48.63 Mbps. Although the computation time increases more rapidly than the zero-knowledge proof generation time when the prover count increases, computation stage demands more frequent communication, our implementation still maintains a relatively reasonable overheads in total, compared with the single-prover baseline.

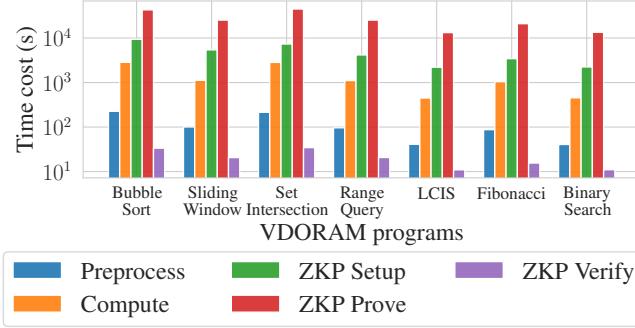

**Program Examples of VDORAM.** To evaluate VDORAM’s applicability, we implemented seven example programs as shown in Figure 11: bubble sort, sliding window, set intersection, range query, longest continuous increasing subsequence (LCIS), Fibonacci, and binary search, highlighting VDORAM’s versatility in handling various computational patterns.

Fig. 11. Time costs of VDORAM procedures for programs (2 provers).

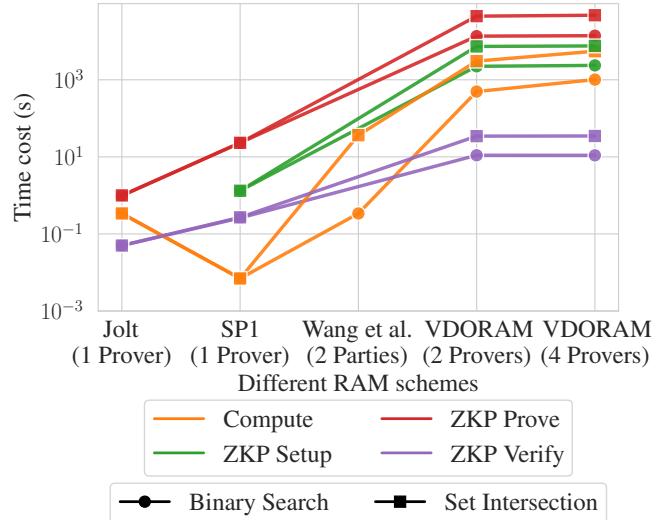

**Comparison of VDORAM.** We compared VDORAM with prior RAM systems: Jolt [3], SP1 [60], and Wang et al. [74]. Table III highlights the feature differences, emphasizing VDORAM’s unique ability to support both public verifiability and distributed obliviousness for an arbitrary number of provers.

TABLE III

COMPARISON OF VDORAM WITH PRIOR WORKS

| RAM System           | Number of Parties | Public Verifiability | Distributed Obliviousness |

|----------------------|-------------------|----------------------|---------------------------|

| Jolt [3]             | 1 prover          | Yes                  | No                        |

| SP1 [60]             | 1 prover          | Yes                  | No                        |

| Wang et al. [74]     | 2 parties         | No                   | Yes                       |

| <b>VDORAM (ours)</b> | $\geq 1$ provers  | Yes                  | Yes                       |

We also conducted an experimental comparison on set intersection and binary search programs. Figure 12 shows the time costs for each system’s main procedures. The results indicate that VDORAM’s additional overhead is justified by its multi-prover and proof generation capabilities.

## VI. CONCLUSION AND FUTURE WORK

In this research, we have introduced CompatCircuit, a novel multi-prover ZKP front-end system. CompatCircuit combines collaborative zkSNARKs with a dishonest-majority MPC framework, facilitating the creation of multi-prover ZKP applications. Building upon CompatCircuit, we have

Fig. 12. Performance comparison of VDORAM with prior works on set intersection and binary search programs. In this figure, the compute procedure of Wang et al. and VDORAM also contains preprocessing time costs. Jolt does not require ZKP setup procedure.